#### Errata

Title & Document Type: 3588A Service Manual

Manual Part Number: 03588-90017

Revision Date: February 1995

### **HP References in this Manual**

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. The HP XXXX referred to in this document is now the Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

### **About this Manual**

We've added this manual to the Agilent website in an effort to help you support your product. This manual provides the best information we could find. It may be incomplete or contain dated information, and the scan quality may not be ideal. If we find a better copy in the future, we will add it to the Agilent website.

## **Support for Your Product**

Agilent no longer sells or supports this product. You will find any other available product information on the Agilent Test & Measurement website:

### www.tm.agilent.com

Search for the model number of this product, and the resulting product page will guide you to any available information. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available.

# **HP 3588A Service Manual**

Serial Number 3005A00647 and greater.

Manual Backdating adapts this manual to instruments with earlier serial numbers.

HP Part Number: 03588-90017 Microfiche Part Number: 03588-90217 Printed in U.S.A.

Print Date: February 1995

©Hewlett-Packard Company, 1990, 1991, 1995. All rights reserved. 8600 Soper Hill Road, Everett, WA 98205-1298 U.S.A.

### **SAFETY SUMMARY**

The following general safety precautions must be observed during all phases of operation, service, and repair of this instrument. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the instrument. Hewlett-Packard Company assumes no liability for the customer's failure to comply with these requirements. This is a Safety Class 1 instrument.

### **GROUND THE INSTRUMENT**

To minimize shock hazard, the instrument chassis and cabinet must be connected to an electrical ground. The instrument is equipped with a three-conductor ac power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE

Do not operate the instrument in the presence of flammable gases or fumes. Operation of any electrical instrument in such an environment constitutes a definite safety hazard.

### **KEEP AWAY FROM LIVE CIRCUITS**

Operating personnel must not remove instrument covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

### DO NOT SERVICE OR ADJUST ALONE

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

### DO NOT SUBSTITUTE PARTS OR MODIFY INSTRUMENT

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the instrument. Return the instrument to a Hewlett-Packard Sales and Service Office for service and repair to ensure the safety features are maintained.

### DANGEROUS PROCEDURE WARNINGS

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

Warning

Dangerous voltages, capable of causing death, are present in this instrument. Use extreme caution when handling, testing, and adjusting.

### **SAFETY SYMBOLS**

General Definitions of Safety Symbols Used On Equipment or In Manuals.

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect against damage to the instrument.

Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1000 volts must be so marked.)

Protective conductor terminal. For protection against electrical shock in case of a fault. Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment.

Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as well as providing protection against electrical shock in case of a fault. A terminal marked with this symbol must be connected to ground in the manner described in the installation (operating) manual, and before operating the equipment

A OR →

Frame or chassis terminal. A connection to the frame (chassis) of the equipment which normally includes all exposed metal structures.

Alternating current (power line.)

Direct current (power line.)

Alternating or direct current (power line.)

### Warning

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, condition or the like, which if not correctly performed or adhered to, could result in injury or death to personnel.

#### Caution

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, condition or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product.

# Note

The NOTE sign denotes important information. It calls attention to procedure, practice, condition or the like, which is essential to highlight.

# **Table of Contents**

| Section I Adjustments                           |

|-------------------------------------------------|

| Introduction                                    |

| Safety Considerations                           |

| Equipment Required                              |

| Remote Operation                                |

| 1. Oven Shutdown                                |

| 2. 80 MHz Reference VCXO                        |

| 3. 300 MHz Reference VCO                        |

| 4. Interpolation VCO                            |

| 5. Single Loop Control Voltage Clamps           |

| 6. 100 kHz and API Spurs                        |

| 7. Sum VCO Filter                               |

| 8. Multiple Loop Control Voltage Clamps         |

| 9. Step VCO Filter                              |

| 10. Pretune Offset and Slope                    |

| 11. ADC Gain, Offset, and Reference             |

| 12. Second IF Bandpass Filter                   |

| 13. Source Bandpass Filter                      |

| 14. First IF Bandpass Filter                    |

| 15. Autorange Thresholds and 1 Meg Ohm Flatness |

| 16. Oven Frequency                              |

| 17. Calibrator Flatness and Level 1-42          |

| 18. Display                                     |

| Section II Replaceable Parts                    |

| Introduction                                    |

| Ordering Information                            |

| Ordering Non-Listed Parts                       |

| Direct Mail Order System                        |

| Assemblies                                      |

| Replacing the CPU Assembly                      |

| Replacing the Memory Assembly                   |

| Cables                                          |

| Hardware                                        |

| Disassembly/Assembly                            |

# Table of Contents (Continued)

| Sect | ion III Manual Backdating            |

|------|--------------------------------------|

|      | Introduction                         |

|      | Manual Changes Supplement            |

|      | Manual Changes Instructions          |

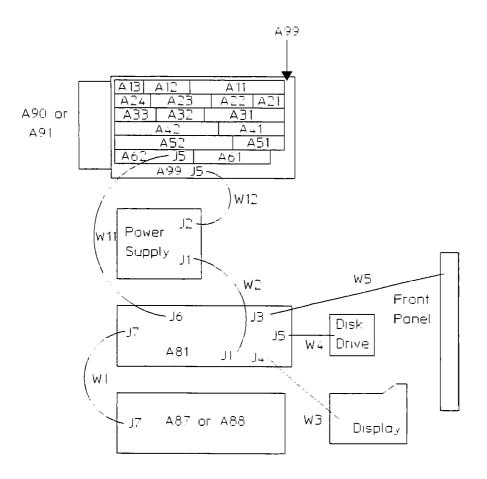

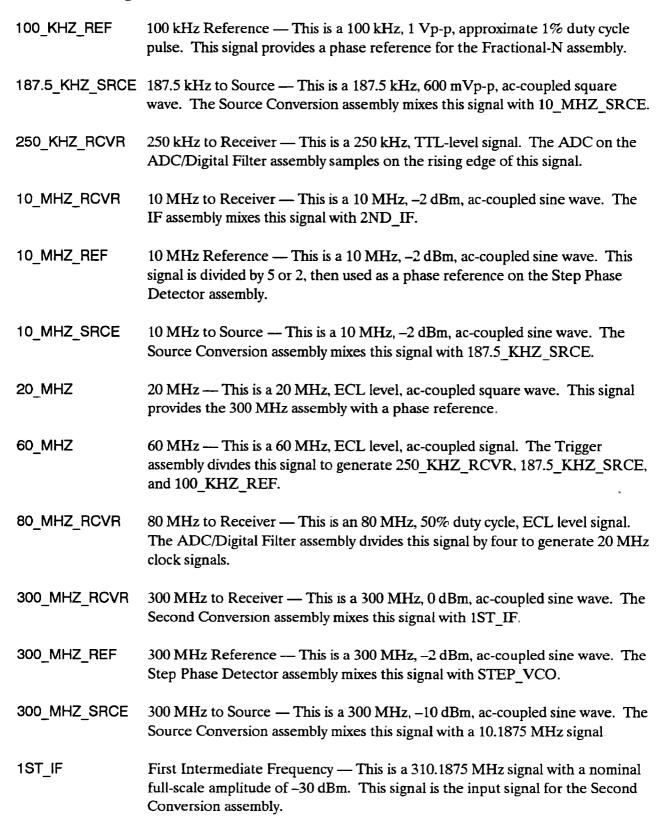

| Sect | ion IV Circuit Descriptions          |

|      | Introduction                         |

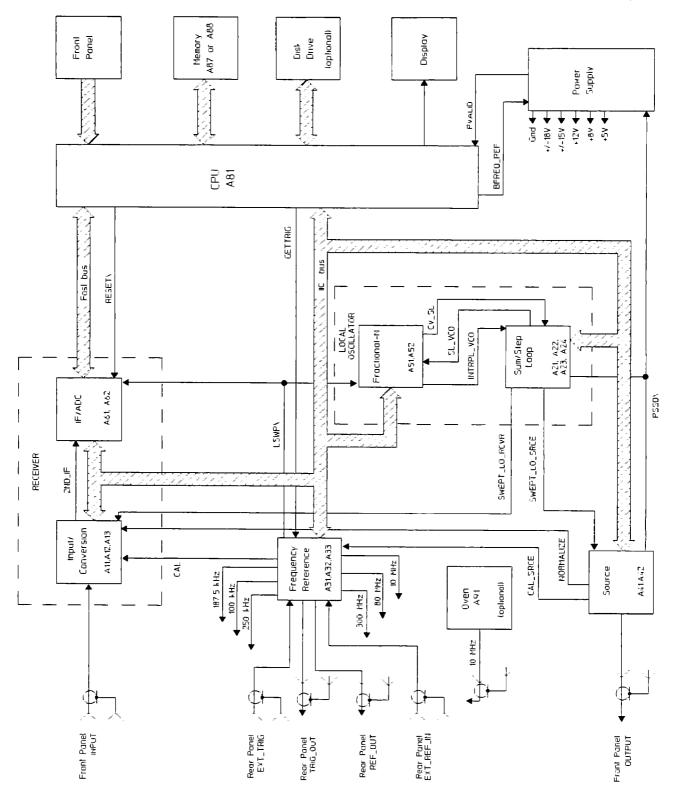

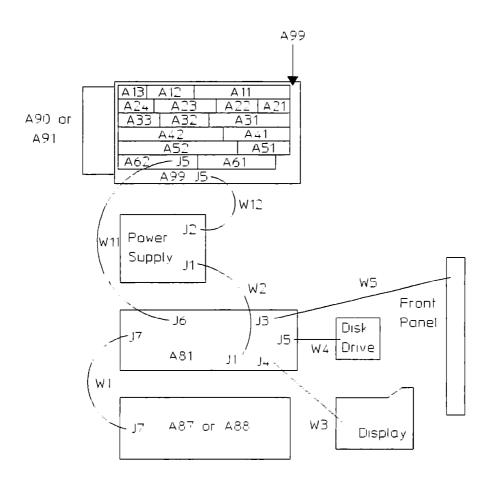

|      | Overall Instrument Description       |

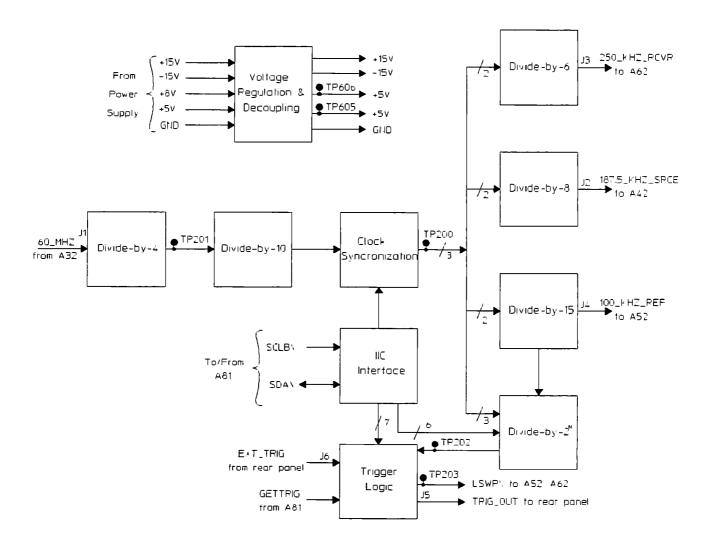

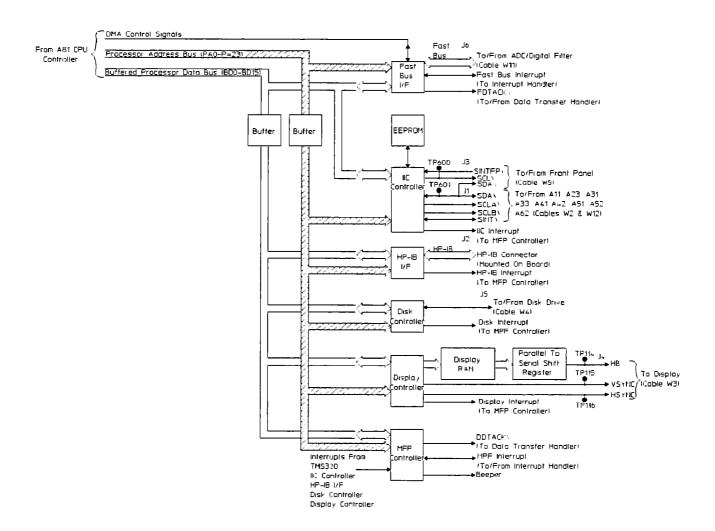

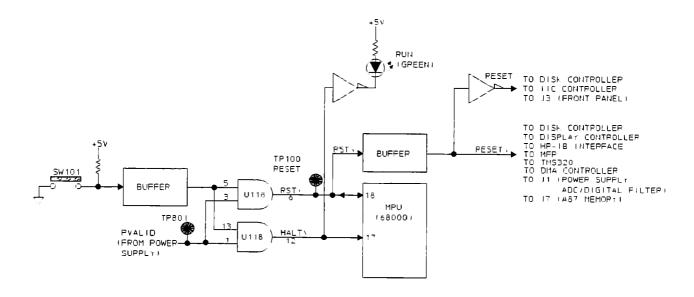

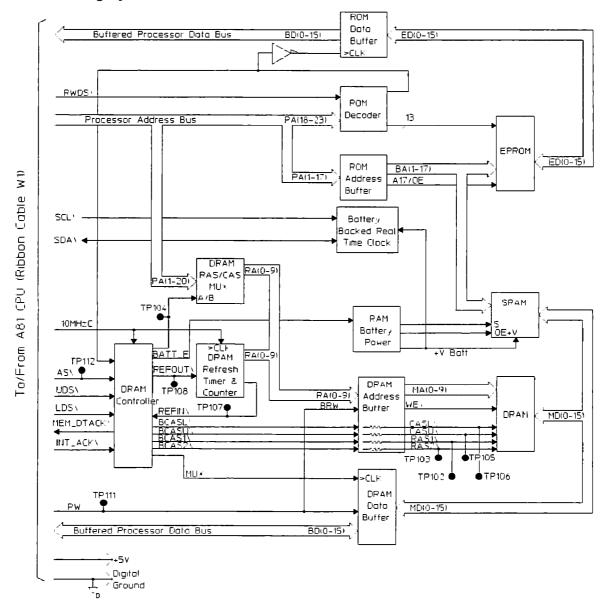

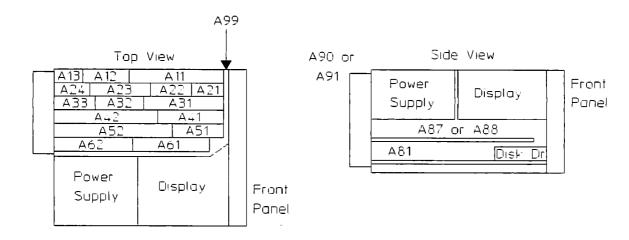

|      | Overall Block Diagram                |

|      | Assemblies                           |

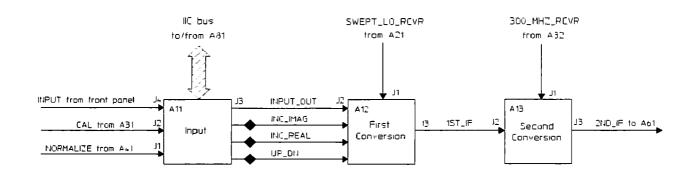

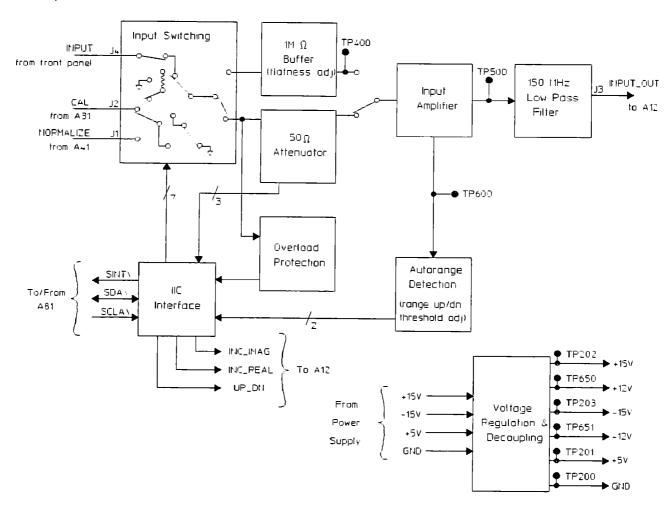

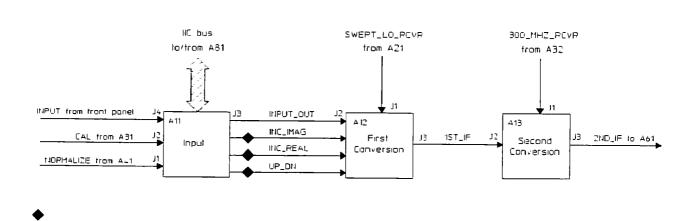

|      | A11 Input                            |

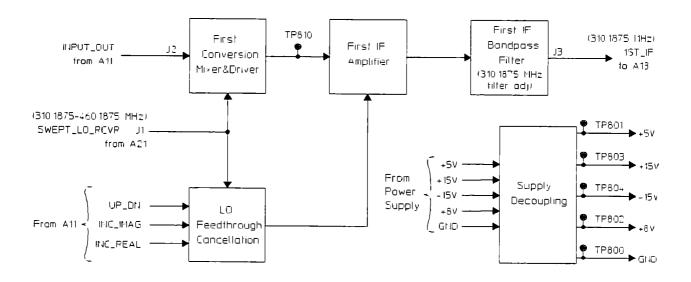

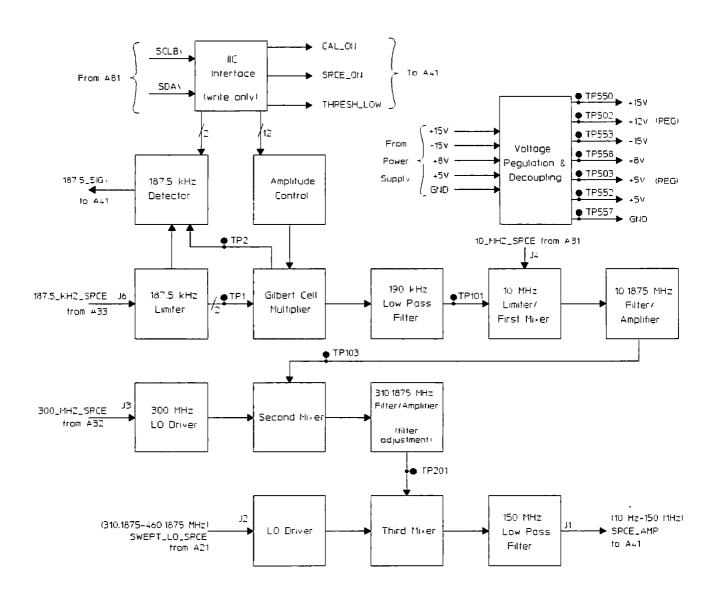

|      | A12 First Conversion                 |

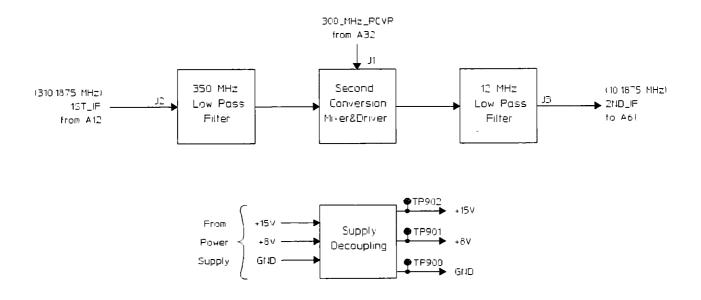

|      | A13 Second Conversion                |

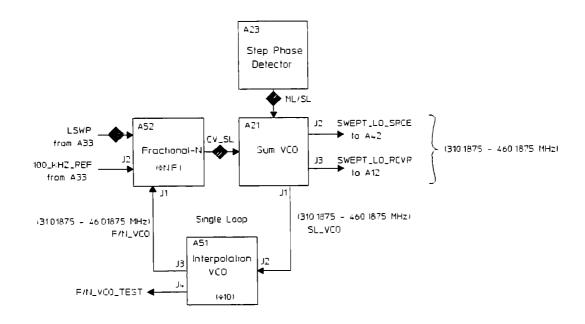

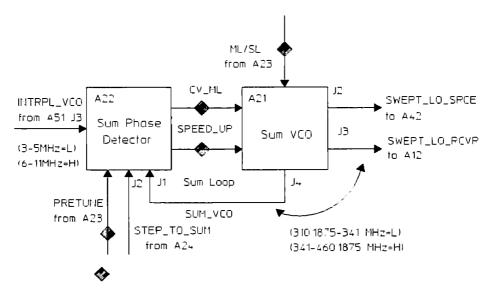

|      | A21 Sum VCO                          |

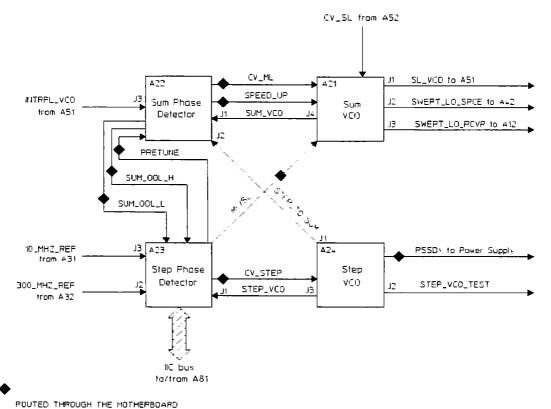

|      | A22 Sum Phase Detector               |

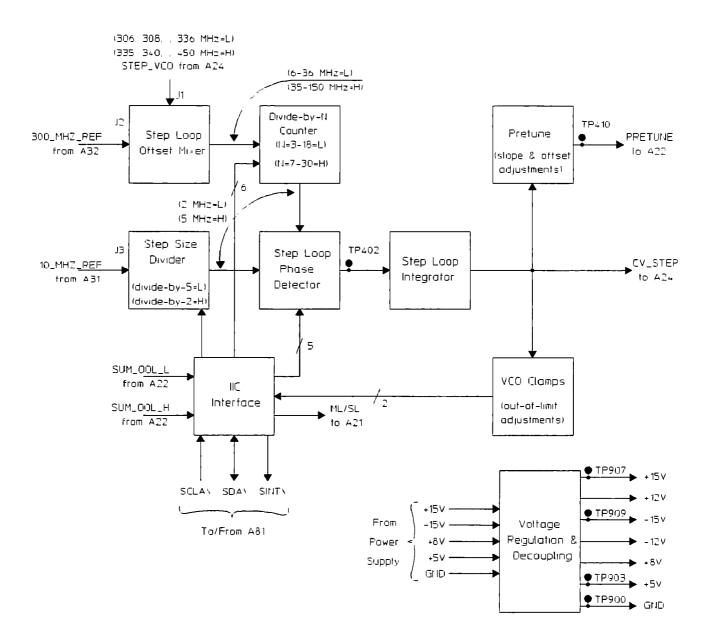

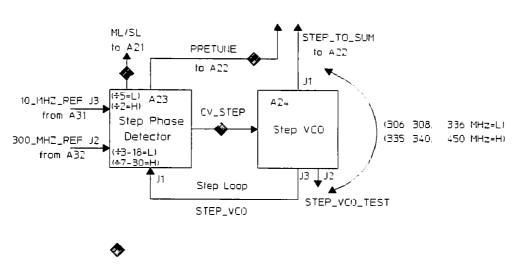

|      | A23 Step Phase Detector              |

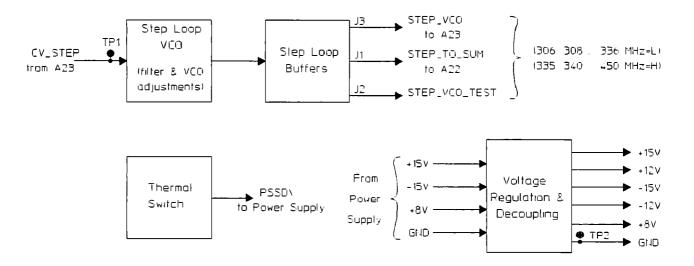

|      | A24 Step VCO                         |

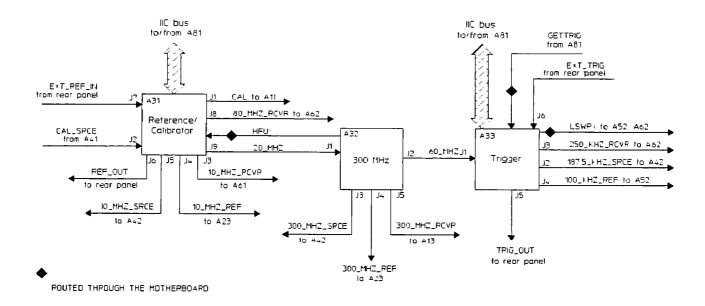

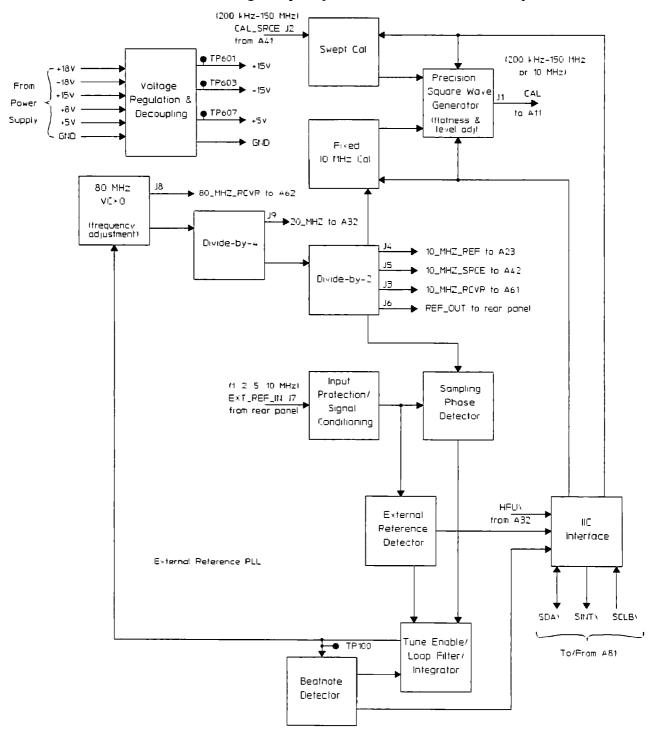

|      | A31 Reference/Calibrator             |

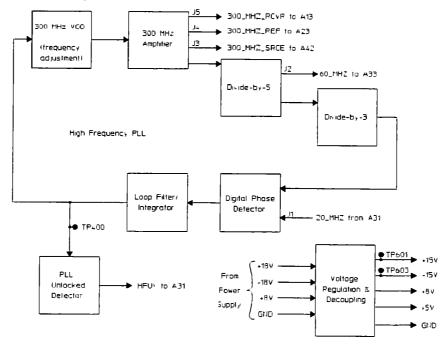

|      | A32 300 MHz                          |

|      | A33 Trigger                          |

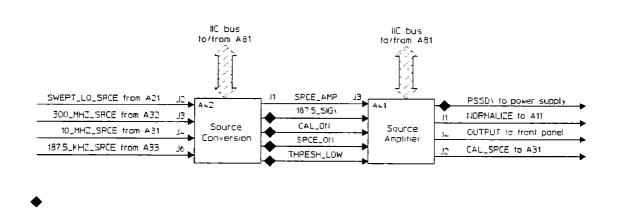

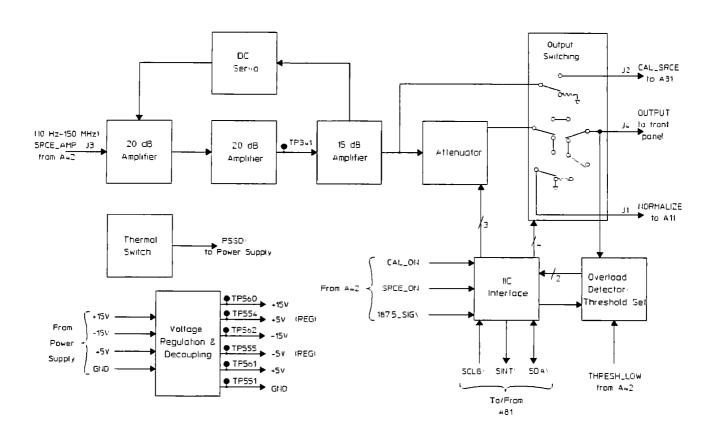

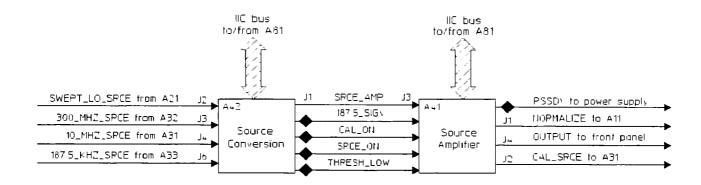

|      | A41 Source Amplifier                 |

|      | A42 Source Conversion                |

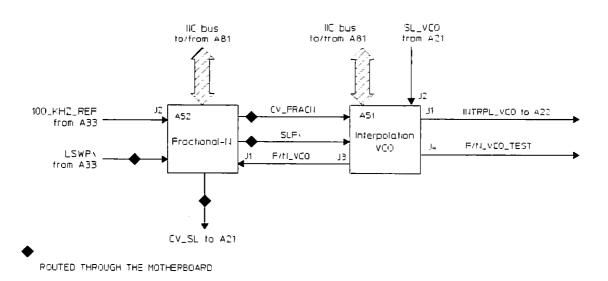

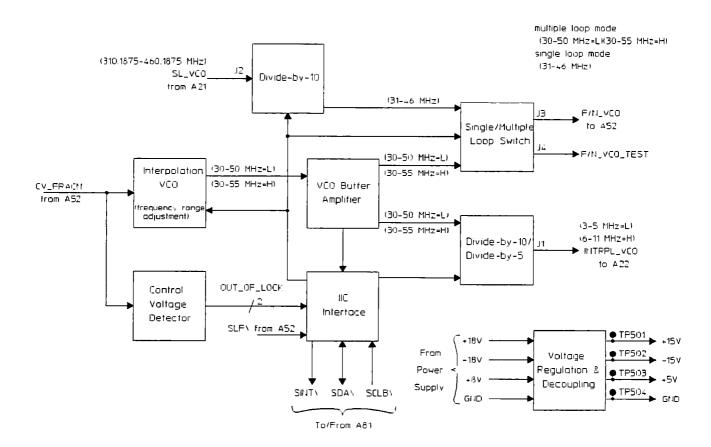

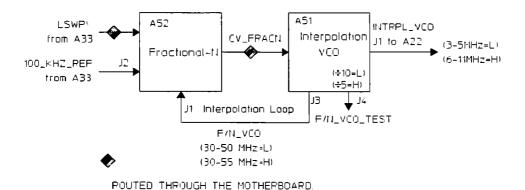

|      | A51 Interpolation VCO                |

|      | A52 Fractional-N                     |

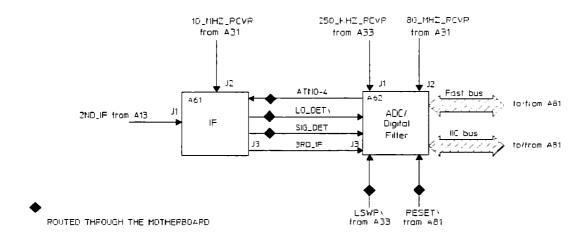

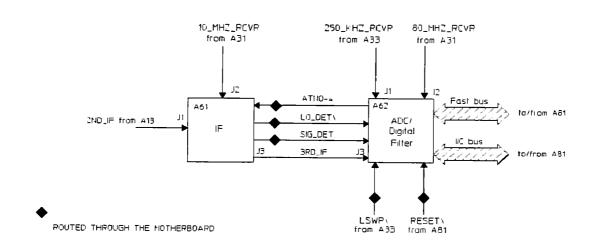

|      | A61 IF                               |

|      | A62 ADC/Digital Filter               |

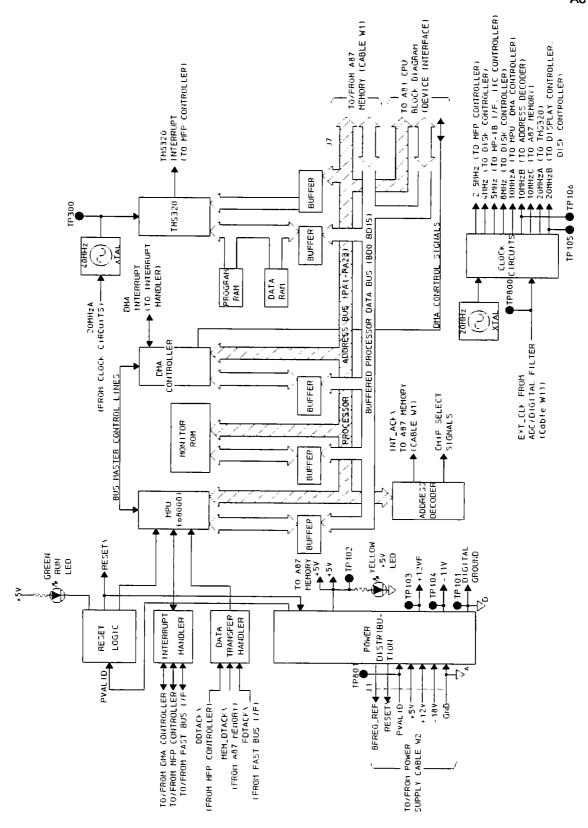

|      | A81 CPU                              |

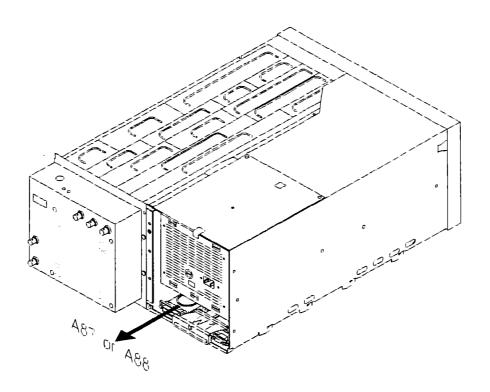

|      | A87 Memory and A88 Expanded Memory   |

|      | A90 Fan Power and A91 Fan Power/Oven |

|      | A99 Motherboard                      |

|      | Front Panel                          |

|      | Power Supply                         |

|      | Disk Drive                           |

|      | Display                              |

|      | Voltage and Signal Distribution      |

|      | W1 Memory Cable Signals              |

|      | W2 CPU Power Cable Signals           |

|      | W3 Display Cable Signals             |

|      | W4 Disk Drive Cable Signals          |

|      | W5 Front Panel Cable Signals         |

|      | W11 Fast Bus Cable Signals           |

|      | W12 Motherboard Power Cable Signals  |

|      | P.F. Cable Signals 4-60              |

| Motherboard Signals                      | 4-73   |

|------------------------------------------|--------|

| HP-IB Connector Signals                  | 4-76   |

| Calibration Routine                      | 4-77   |

| Calibration Error Message                | 4-78   |

| Calibration Correction Curves            | 4-79   |

| Fault Log Messages                       | 4-82   |

| Power-On and Preset States               | 4-84   |

| Power-On States                          | 4-86   |

| Nonvolatile States                       | . 4-86 |

| Section V Service                        |        |

| Introduction                             | 5-1    |

| Safety Considerations                    | . 5-1  |

| Equipment Required                       | . 5-2  |

| How to Use This Section                  | 5-2    |

| Troubleshooting Hints                    | . 5-3  |

| Choosing a Troubleshooting Test          | 5-4    |

| What to Do After an Assembly Is Replaced | 5-5    |

| Initial Verification                     | 5-8    |

| Test 1. Initial Verification             | 5-8    |

| Troubleshooting Using the Power-On Test  | 5-14   |

| Test 2. Power-on                         | 5-14   |

| Test 3. CPU, Memory, and Buses           | 5-17   |

| Test 4. Memory                           | 5-19   |

| Test 5. Display                          | 5-20   |

| Test 6. IIC Bus (Inter-IC Bus)           | 5-23   |

| Test 7. Fast Bus                         | 5-26   |

| Test 8. Control Lines                    | 5-28   |

| Troubleshooting Using the Self Tests     | 5-30   |

| Test 9. Self Test                        | 5-31   |

| Test 10. ALL Locks Analyzer              | 5-36   |

| Test 11. Disk Drive                      | 5-38   |

| Test 12. HP-IB/RS-232                    | 5-41   |

| Test 13. Digital Filter                  | 5-42   |

| Test 14. Source                          | 5-43   |

| Test 15. Local Oscillator                | 5-46   |

| Test 16. Interpolation Loop              | 5-47   |

| Test 17. Single Loop                     | 5-49   |

| Test 18. Input Conversion                | 5-52   |

| Test 19. Sum Loop                        | 5-58   |

| Test 20. Step Loop                       | 5-61   |

| Test 21. Reference                       | 5-63   |

| Test 22. Intermittent Failures           | 5-66   |

# Table of Contents (Continued)

| Troubleshooting Failing Performance Tests                 |

|-----------------------------------------------------------|

| Test 23. Local Oscillator Feedthrough                     |

| Test 24. Phase Noise                                      |

| Test 25. Residual Responses                               |

| Test 26. Noise Level                                      |

| Test 27. Frequency Accuracy                               |

| Test 28. Spurious Responses                               |

| Test 29. Input Harmonic Distortion                        |

| Test 30. Intermodulation Distortion                       |

| Test 31. Source Amplitude Accuracy and Frequency Response |

| Test 32. Log Scale Accuracy                               |

| Troubleshooting Miscellaneous Failures                    |

| Test 33. Memory Battery5-8                                |

| Test 34. Fan Power                                        |

| Test 35. Trigger                                          |

| Power-on Test Descriptions                                |

| Low-level Tests                                           |

| High-level Test                                           |

| Power-on Test Messages                                    |

| Self-Test Descriptions                                    |

| Self Tests that Perform a Measurement                     |

| Individual Self-Test Descriptions 5 or                    |

## Index

# Section I

# **Adjustments**

### Introduction

This section contains the adjustment procedures for the HP 3588A Spectrum Analyzer. Use these adjustments if the analyzer does not meet its specifications or if instructed in section V, "Service," to perform these adjustments. These adjustments are not required for routine maintenance. Table 1-1 lists all the adjustments.

The top cover must be removed to perform all adjustments except "1. Oven Shutdown" and "16. Oven Frequency." For information on top cover removal, see "Disassembly/Assembly" in section II, "Replaceable Parts."

# Note

Allow the HP 3588A Spectrum Analyzer to warm up for at least an hour. This is critical for adjustment "2. 80 MHz Reference VCXO." Analyzers with the oven option (option 001) must cool off for at least 8 hours before doing adjustment "1. Oven Shutdown" and warm up for at least 48 hours before doing adjustment "16. Oven Frequency."

During many of these adjustment procedures, an adjustment message appears on the screen. The instructions on the screen are not as complete as the instructions in this manual. When an adjustment message appears on the screen, continue to follow the instructions in this manual. Failure to follow the instructions in this manual may result in an incorrect adjustment, which would appear as a hardware failure.

Table 1-1. Adjustments

| Adjustment Procedure                           | Assembly | Component                                  |

|------------------------------------------------|----------|--------------------------------------------|

| 1. Oven Shutdown                               | A91      | R2                                         |

| 2 80 MHz Reference VCXO                        | A31      | C6, R13                                    |

| 3 300 MHz Reference VCO                        | A32      | L506, L508                                 |

| 4 Interpolation VCO                            | A51      | L101                                       |

| 5 Single Loop Control Voltage Clamps           | A52      | R423, R422                                 |

| 6 100 kHz and API Spurs                        | A52      | R416, R518, R521, R533                     |

| 7 Sum VCO Filter                               | A21      | L106, L107                                 |

| 8 Multiple Loop Control Voltage Clamps         | A23      | R463, R461                                 |

| 9 Step VCO Filter                              | A24      | L506, 507                                  |

| 10. Pretune Offset and Slope                   | A23      | R452, R457                                 |

| 11 ADC Gain, Offset, and Reference             | A62      | R407, R405, R431                           |

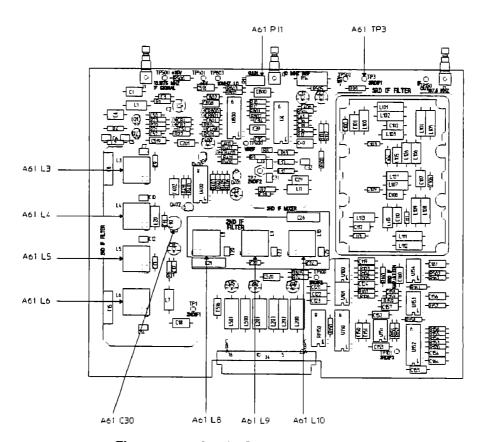

| 12. Second IF Bandpass Filter                  | A61      | L3-L6, L8-L10, C30, R11                    |

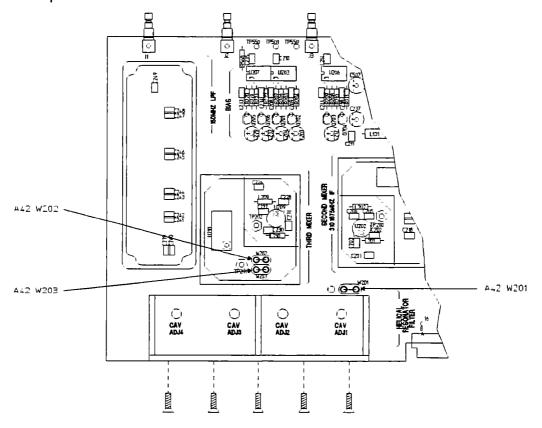

| 13 Source Bandpass Filter                      | A42      | CAV ADJ 1-CAV ADJ4                         |

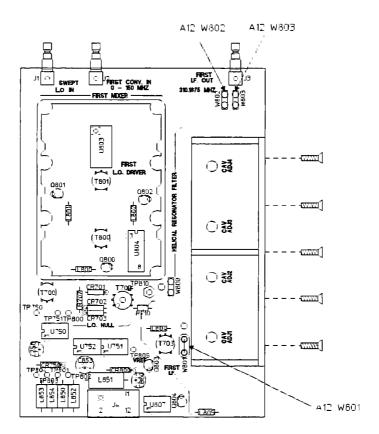

| 14 First IF Bandpass Filter                    | A12      | CAV ADJ 1-CAV ADJ4                         |

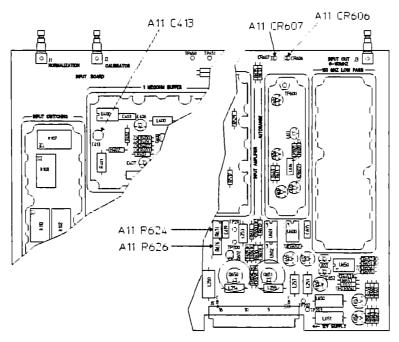

| 15 Autorange Thresholds and 1 Meg Ohm Flatness | A11      | C413, R624, R626                           |

| 16. Oven Frequency                             | A91      | U3, R12                                    |

| 17 Calibrator Flatness and Level               | A31      | R322, C330                                 |

| 18 Display                                     | Display  | VR31-VR34, VR41, VR42, VR64,<br>VR67, L403 |

If an assembly is replaced, see table 5-2 for required adjustments and performance tests.

# **Safety Considerations**

Although the HP 3588A Spectrum Analyzer is designed in accordance with international safety standards, this manual contains information, cautions, and warnings that must be followed to ensure safe operation and to keep the unit in safe condition. Adjustments in this section are performed with power applied and protective covers removed. These adjustments must be performed by trained service personnel who are aware of the hazards involved (such as fire and electrical shock).

# Warning

Any interruption of the protective (grounding) conductor inside or outside the unit, or disconnection of the protective earth terminal can expose operators to potentially dangerous voltages.

Under no circumstances should an operator remove any covers, screws, shields or in any other way access the interior of the HP 3588A Spectrum Analyzer. There are no operator controls inside the analyzer.

# **Equipment Required**

See chapter 1, "General Information," in the HP 3588A Performance Test Guide for tables listing recommended test equipment. Any equipment which meets the critical specifications given in the tables may be substituted for the recommended model.

# **Remote Operation**

Adjustments can be set up using the remote operation capability of the HP 3588A Spectrum Analyzer. See table 1-2 for a list of adjustments and corresponding HP-IB codes. See the HP 3588A HP-IB Programming Reference for general information on remote operation.

Table 1-2. HP-IB Codes to Set Up Adjustments

| Adjustments                                     | HP-IB Codes                                                                               |

|-------------------------------------------------|-------------------------------------------------------------------------------------------|

| 4. Interpolation VCO                            | DIAG:FRAC:VCO ADJ                                                                         |

| 5. Single Loop Control Voltage Clamps           | DIAG:FRAC:SLO:CHIG<br>DIAG:FRAC:SLO:CLOW                                                  |

| 6. 100 kHz and API Spurs                        | DIAG:FRAC:SPUR:NULL DIAG:FRAC:SPUR:API:ONE DIAG:FRAC:SPUR:API:TWO DIAG:FRAC:SPUR:API:FOUR |

| 7 Sum VCO Filter                                | DIAG:FRAC:SUMV:LPF                                                                        |

| 8 Multiple Loop Control Voltage Clamps          | DIAG:FRAC:MLO:CHIG<br>DIAG:FRAC:MLO:CLOW                                                  |

| 9 Step VCO Filter                               | DIAG:FRAC:SVCO:LPF                                                                        |

| 10 Pretune Offset and Slope                     | DIAG:FRAC:PRET:OFFS<br>DIAG:FRAC:PRET:SLOP                                                |

| 11 ADC Gain, Offset, and Reference              | DIAG:ADJ:ADC:GAIN<br>DIAG:ADJ:ADC:OFFS                                                    |

| 12 Second IF Bandpass Filter                    | DIAG:REC:TWO:ONE DIAG:REC:TWO:TWO DIAG:REC:TWO:THR DIAG:REC:TWO:FOUR DIAG:REC:TWO:FIVE    |

| 13. Source Bandpass Filter                      | DIAG:ADJ:SOUR:RES                                                                         |

| 14. First IF Bandpass Filter                    | DIAG:REC:HRES                                                                             |

| 15. Autorange Thresholds and 1 Meg Ohm Flatness | DIAG:REC:MOHM:FLAT<br>DIAG:REC:RANG UP<br>DIAG:REC:RANG DOWN                              |

| 17. Calibrator Flatness and Level               | DIAG:CAL:EREF<br>DIAG:CAL:FLAT<br>DIAG:CAL:HFR<br>DIAG:CAL:LEV                            |

| 18. Display                                     | TEST:DISP PATT                                                                            |

### 1. Oven Shutdown

This procedure adjusts the heater shutdown trip point on the optional A91 Fan Power/Oven assembly. When the oven is cold, the heater shutdown circuit disconnects the oven output from the rear panel output connector. After the oven has been on long enough for the frequency to be stable, the heater shutdown circuit connects the oven output to the rear panel output connector.

Equipment Required:

Spectrum Analyzer

**BNC Cable**

# Note

The HP 3588A Spectrum Analyzer must be off for at least 8 hours before this adjustment is made. Once power is applied, the adjustment MUST be completed within FIVE MINUTES.

- 1. Remove the screw on the oven-adjustment cover. Lift the screw side of the oven-adjustment cover and tilt back to the open position.

- 2. Connect the spectrum analyzer to the OVEN REF OUT connector (located on rear panel) using a BNC cable.

- 3. Set the spectrum analyzer as follows:

Center Frequency 10 MHz

Frequency Span 1 MHz

Reference Level -60 dBm

- 4. Set the power switch to ON (1), then check that the amplitude of the 10 MHz signal is approximately 70 dBm or lower (oven is cold).

- 5. Change the reference level on the spectrum analyzer to 10 dBm.

- 6. Turn OVEN SHUTDOWN (A91 R2) counterclockwise until the amplitude of the 10 MHz signal is > 0 dBm. Then turn OVEN SHUTDOWN clockwise until the amplitude of the signal just returns to approximately 70 dBm and turn an additional 10 degrees clockwise.

- 7. Return the oven-adjustment cover and screw, and rear panel jumper (OVEN REF OUT to EXT REF IN) to their original positions.

## 2. 80 MHz Reference VCXO

This procedure adjusts the control voltage for the 80 MHz reference VCXO on the A31 Reference/Calibrator assembly. The 80 MHz reference is the primary frequency reference for the analyzer.

**Equipment Required:**

Frequency Counter

BNC(m)-to-SMB(f) Cable Flat-Edge Adjustment Tool

Note

Before doing this adjustment, make sure the HP 3588A Spectrum Analyzer has been ON (1) for approximately one hour to allow the 80 MHz reference VCXO to reach a stable operating temperature.

- 1. Disconnect the rear panel jumper (OVEN REF OUT to EXT REF IN) on analyzers with the optional oven.

- 2. Disconnect the cable from A31 J3, and connect the frequency counter to A31 J3 using a BNC-to-SMB cable.

- 3. Adjust FREQ ADJ FINE (A31 R13) to the center of its adjustment range.

- 4. Adjust FREQ ADJ CRS (A31 C6) for 10 MHz ± 10 Hz using the flat-edge adjustment tool in the service kit.

- 5. Adjust FREQ ADJ FINE for  $10 \text{ MHz} \pm 1 \text{ Hz}$ .

- 6. Disconnect the frequency counter from A31 J3, and reconnect the cable from A61 J2 to A31 J3.

- 7. Reconnect the rear panel jumper on analyzers with the optional oven.

## 3. 300 MHz Reference VCO

This procedure adjusts the control voltage for the 300 MHz reference VCO on the A32 300 MHz assembly. The 300 MHz reference is the high-frequency reference for the analyzer.

Equipment Required:

Digital Multimeter

Extender Board Extender Cable

- 1. Set the power switch to STANDBY (a). Remove the screw at each end of the A32 300 MHz assembly, and place the assembly on an extender board.

- 2. Reconnect A32 J1 to A31 J9 using an extender cable.

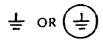

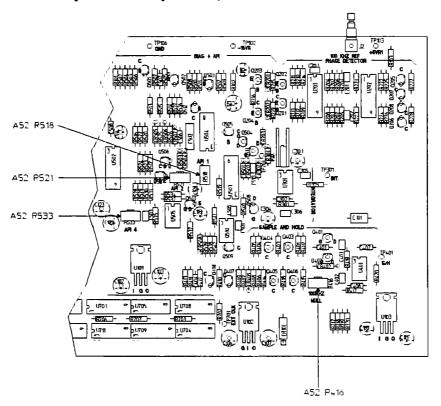

- 3. Connect the multimeter's input terminal to A32 TP400 (see figure 1-1) and its ground terminal to chassis ground.

Figure 1-1. A32 300 MHz Component Locator

Adjustments HP 3588A

### 3. 300 MHz Reference VCO

4. Set the power switch to ON (1). Through the holes in shield can, alternately adjust A32 L506 and L508 for  $-7.00 \pm 0.25$ V.

- 5. Set the power switch to STANDBY (a). Place the 300 MHz assembly into the card nest and replace the screws.

- 6. Reconnect the following using original cables:

A32 J1 to A31 J9

A32 J2 to A33 J1

A32 J3 to A42 J3

A32 J4 to A23 J2

A32 J5 to A13 J1

# 4. Interpolation VCO

This procedure adjusts the frequency range of the interpolation VCO on the A51 Interpolation VCO assembly.

Equipment Required:

Frequency Counter

Extender Board

BNC(m)-to-SMB(f) Cable

- 1. Set the power switch to STANDBY (a). Remove the screw at each end of the A51 Interpolation VCO assembly, and remove the assembly from the card nest.

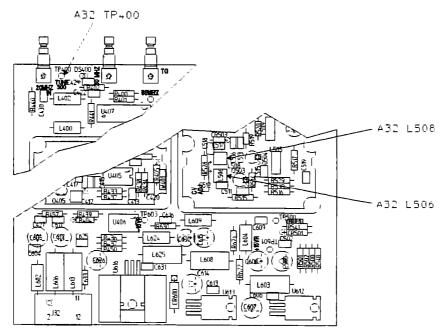

- 2. Move the jumper on A51 J101 to its test position (see figure 1-2). Place the assembly on an extender board.

Figure 1-2. A51 Interpolation VCO Component Locator

Adjustments HP 3588A

- 4 Interpolation VCO

- 3. Connect the frequency counter to A51 J4 using a BNC-to-SMB cable.

- 4. Set the power switch to ON (1), then press the following keys:

```

[ Spci Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ LOCAL OSC ]

[ INTRPL VCO ]

```

- 5. Through the hole in the shield can, adjust A51 L101 for  $55 \pm 0.5$  MHz using a plastic tuning tool.

- 6. Set the power switch to STANDBY (a). Move the jumper back to its normal position, and place the Interpolation VCO assembly into the card nest. Replace the screws.

- 7. Reconnect the following using original cables:

```

A51 J1 to A22 J3

A51 J2 to A21 J1

A51 J3 to A52 J1

A51 J4 (no connection)

```

# 5. Single Loop Control Voltage Clamps

This procedure adjusts the upper and lower out-of-limit voltages on the A52 Fractional-N assembly. The single loop control voltage is compared to the out-of-limit voltages. If the control voltage exceeds either the upper or lower out-of-limit voltage, the control voltage is clamped to the out-of-limit voltage.

Equipment Required:

Frequency Counter BNC(m)-to-SMB(f) Cable

- 1. Set the power switch to ON (1).

- 2. Disconnect the cable from A21 J3, and connect the frequency counter to A21 J3 using a BNC-to-SMB cable.

- 3. Press the following keys:

```

[ Spcl Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ LOCAL OSC ]

[ SNGL LOOP CLAMPS

[ SNGL LOOP CLAMP-HI ]

```

- 4. Disconnect the cable from A51 J3.

- 5. Adjust H.F.LIMIT (A52 R423) for 470 ± 2 MHz. If H.F.LIMIT cannot be adjusted to 470 ± 2 MHz, disconnect and reconnect A51 J3 until the loop unlocks and H.F.LIMIT can be adjusted.

- 6. Reconnect the cable from A51 J3 to A52 J1.

- 7. Press the [SNGL LOOP CLAMP-LOW] softkey.

- 8. Disconnect the cable from A52 J2.

- 9. Adjust L.F.LIMIT (A52 R422) for  $290 \pm 2$  MHz.

- 10. Disconnect the frequency counter from A21 J3.

- 11. Reconnect A21 J3 to A12 J1 and A52 J2 to A33 J4.

# 6. 100 kHz and API Spurs

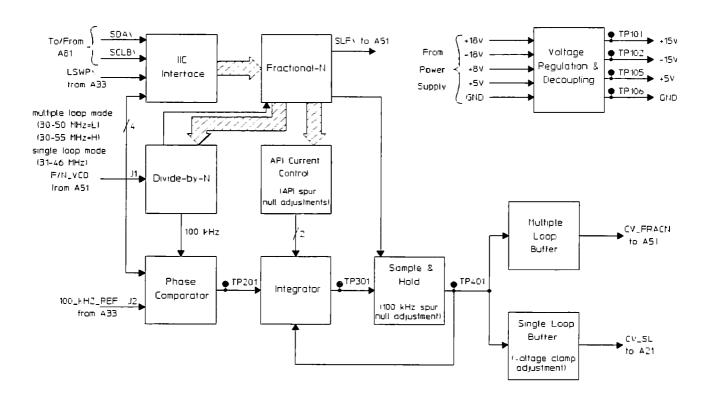

This procedure attenuates the 100 kHz sample and hold spur, and the API spurs on the A52 Fractional-N assembly.

**Equipment Required:**

Spectrum Analyzer

Extender Board Extender Cables

BNC(m)-to-SMB(f) Cable

**BNC** Cable

1. Set the power switch to STANDBY (a). Remove the screw at each end of the A52 Fractional-N assembly, and place the assembly on an extender board.

### Caution

To avoid damaging the cables connected to A33 J5 and J6, disconnect and position the cables away from the A52 Fractional-N assembly before removing or inserting the A52 Fractional-N assembly.

2. Reconnect the following using extender cables:

A52 J1 to A51 J3 A52 J2 to A33 J4 A62 J1 to A33 J3 A62 J2 to A31 J8

- 3. Disconnect the cable from A21 J2, and connect the spectrum analyzer to A21 J2 using a BNC-to-SMB cable. Connect the spectrum analyzer's 10 MHz reference output to EXT REF IN (on rear panel) using a BNC cable.

- 4. Press the [ Preset ] hardkey, then set the spectrum analyzer as follows:

Center Frequency 400 MHz

Frequency Span 500 kHz

Reference Level 10 dBm

Res BW 10 kHz

Video BW 1 kHz

5. Set the power switch to ON (1), then press the following keys:

```

[ Spci Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ LOCAL OSC ]

[ SPURS ]

```

[ 100 kHz ]

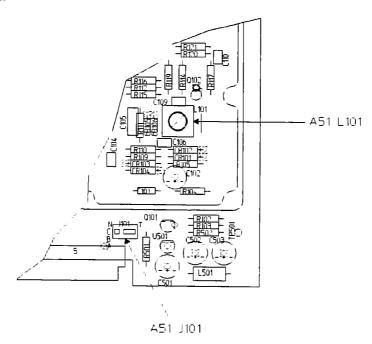

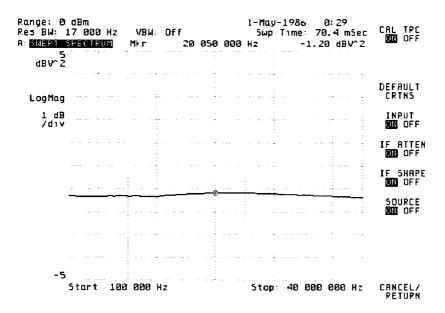

6. Adjust A52 R416 (see figure 1-3) for a minimum spur level at approximately 400.2 MHz (figure 1-4 shows the spurs out of adjustment).

Figure 1-3. A52 Fractional-N Component Locator

Figure 1-4. Spurs Out of Adjustment

Adjustments HP 3588A

- 6. 100 kHz and API Spurs

- 7. Set the spectrum analyzer as follows:

Center Frequency 400.03 MHz

Frequency Span 25 kHz

Res BW 300 Hz

Video BW 300 Hz

Sweeptime 1 sec

- 8. Press the [API 1] softkey.

- 9. Adjust API 1 (A52 R518) for a minimum spur level at 400.033 MHz.

- 10. Change the spectrum analyzer's center frequency to 400.003 MHz.

- 11. Press the [API 2] softkey.

- 12. Adjust API 2 (A52 R521) for a minimum spur level at 400.006 MHz.

- 13. Change the spectrum analyzer's center frequency to 400.0001 MHz.

- 14. Press the [API 4] softkey.

- 15. Adjust API 4 (A52 R533) for a minimum spur level at 400.00303 MHz.

- 16. Set the power switch to STANDBY (a). Place the Fractional-N assembly into the card nest, and replace the screws.

- 17. Reconnect the following using original cables:

A52 J1 to A51 J3

A52 J2 to A33 J4

A62 J1 to A33 J3

A62 J2 to A31 J8

A21 J2 to A42 J2

A33 J5 to TRIG OUT (white cable)

A33 J6 to EXT TRIG (black cable)

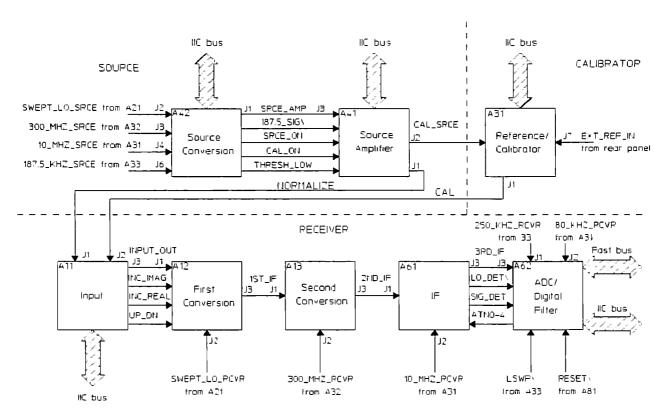

### 7. Sum VCO Filter

This procedure adjusts the low pass filter on the A21 Sum VCO assembly. This filter improves spectral purity of the VCO.

Equipment Required:

Spectrum Analyzer

Extender Board Extender Cable

BNC(m)-to-SMB(f) Cable

- 1. Set the power switch to STANDBY (a). Remove the screw at each end of the A21 Sum VCO assembly, and place the assembly on an extender board.

- 2. Reconnect A21 J1 to A51 J2 using an extender cable. (A11 J2 to A31 J1 may be left unconnected.)

- 3. Connect the spectrum analyzer to A21 J2 using a BNC-to-SMB cable.

- 4. Set the power switch to ON (1), then press the following keys:

```

[ Spci Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ LOCAL OSC ]

[ SUM VCO LOW PASS ]

```

5. Press the [ Preset ] hardkey, then set the spectrum analyzer as follows:

Center Frequency 380 MHz

Frequency Span 200 MHz

Reference Level -5 dBm

dB per Division 1 dB

Maximum Hold On

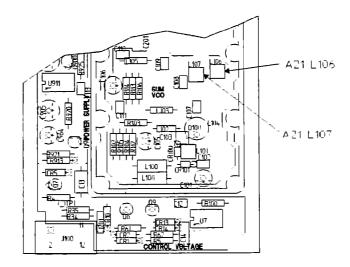

6. Through the holes in the shield can, alternately adjust A21 L106 and L107 (see figure 1-5) for a flatness (maximum amplitude minus minimum amplitude) of less than 3 dB(p-p). During this adjustment, periodically clear the spectrum analyzer's maximum hold function.

Figure 1-5. A21 Sum VCO Component Locator

- 7. Set the power switch to STANDBY (a). Place the Sum VCO assembly into the card nest, and replace the screws.

- 8. Reconnect the following using original cables:

A21 J1 to A51 J2

A21 J2 to A42 J2

A21 J3 to A12 J1

A21 J4 to A22 J1

A11 J2 to A31 J1

# 8. Multiple Loop Control Voltage Clamps

This procedure adjusts the upper and lower out-of-limit voltages on the A23 Step Phase Detector assembly. The multiple loop control voltage is compared to the out-of-limit voltages. If the control voltage exceeds either the upper or lower out-of-limit voltage, the control voltage is clamped to the out-of-limit voltage.

Equipment Required:

Frequency Counter

BNC(m)-to-SMB(f) Cable

- 1. Set the power switch to ON (1).

- 2. Disconnect the cables from A23 J3 and from A24 J1.

- 3. Connect the frequency counter to A24 J1 using a BNC-to-SMB cable.

- 4. Press the following keys:

```

[ Spcl Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ LOCAL OSC ]

[ MULT LOOP CLAMPS ]

[ MULT LOOP CLAMP-LOW ]

```

- 5. Adjust STEP OOL\_L (A23 R461) for  $297 \pm 0.5$  MHz.

- 6. Reconnect the cable from A23 J3 to A31 J4.

- 7. Disconnect the cable from A23 J1.

- 8. Press the [MULT LOOP CLAMP-HI] softkey.

- 9. Adjust STEP OOL H (A23 R463) for  $470 \pm 0.5$  MHz.

- 10. Disconnect the frequency counter from A24 J1.

- 11. Reconnect A23 J1 to A24 J3 and A24 J1 to A22 J2.

- 12. Press the [Preset ] hardkey to exit the adjustment mode.

# 9. Step VCO Filter

This procedure adjusts the low pass filter on the A24 Step VCO assembly. This filter improves the spectral purity of the VCO.

Equipment Required:

Spectrum Analyzer

Extender Board

Extender Cable

BNC(m)-to-SMB(f) Cable

- 1. Connect the spectrum analyzer to A24 J2 using a BNC-to-SMB cable.

- 2. Set the power switch to ON (1), then press the following keys:

```

[ Spcl Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ LOCAL OSC ]

[ STEP VCO LOW PASS ]

```

3. Press the [Preset] hardkey, then set the spectrum analyzer as follows:

Center Frequency 380 MHz

Frequency Span 200 MHz

Reference Level - 20 dBm

dB per Division 1 dB

Maximum Hold On

- 4. If the flatness (maximum amplitude minus minimum amplitude) of the displayed signal is less than 3 dB(p-p), the step VCO filter is within tolerance and should not be adjusted. Disconnect the spectrum analyzer from A24 J2.

- 5. If the flatness (maximum amplitude minus minimum amplitude) of the displayed signal is larger than 3 dB(p-p), do the following:

- a. Set the power switch to STANDBY (b). Remove the screw at each end of the A24 Step VCO assembly, and place the assembly on an extender board.

- b. Reconnect A24 J3 to A23 J1 using an extender cable.

- c. Reconnect the spectrum analyzer to A24 J2 using a BNC-to-SMB cable.

d. Set the power switch to ON (1), then press the following keys:

```

[ Spci Fctn ]

[ ] (second softkey from bottom)

— 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ LOCAL OSC ]

[ STEP VCO LOW PASS ]

```

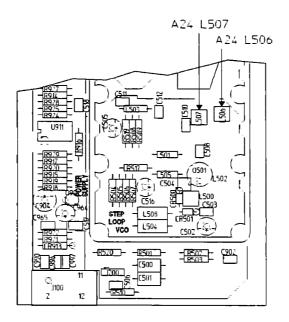

e. Through the holes in the shield can, alternately adjust A24 L506 and L507 (see figure 1-6) for a flatness (maximum amplitude minus minimum amplitude) of less than 3 dB(p-p). During this adjustment, periodically clear the spectrum analyzer's maximum hold function.

Figure 1-6. A24 Step VCO Component Locator

- f. Set the power switch to STANDBY (a). Place the Step VCO assembly into the card nest, and replace the screws.

- g. Reconnect the following using original cables:

A24 J1 to A22 J2 A24 J2 (no connection) A24 J3 to A23 J1

# 10. Pretune Offset and Slope

This procedure adjusts the pretune offset and slope on the A23 Step Phase Detector assembly. Pretune offset is added to the control voltage, then amplified by pretune slope. The resulting voltage coarsely adjusts the sum VCO's frequency to ensure that the sum loop can phase lock.

Equipment Required:

Frequency Counter BNC(m)-to-SMB(f) Cable

- 1. Set the power switch to ON (1).

- 2. Disconnect the cables from A22 J3 and from A21 J3.

- 3. Connect the frequency counter to A21 J3 using a BNC-to-SMB cable.

- 4. Press the following keys:

```

[ SpcI Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ LOCAL OSC ]

```

- 5. Press the [ PRETUNE OFFSET ] softkey.

- 6. Adjust PRETUNE OFFSET (A23 R452) for  $450 \pm 0.5$  MHz.

- 7. Press the [PRETUNE SLOPE] softkey.

- 8. Adjust PRETUNE SLOPE (A23 R457) for  $306 \pm 0.5$  MHz.

# Note

9. Repeat steps 5 through 8 until both PRETUNE OFFSET and PRETUNE SLOPE are within tolerance without adjustment.

10. Press the following keys:

```

[ Preset ]

[ Sweep ]

[ SWEEP AUTO MAN ]

[ MANUAL FREQ ]

30

[ MHz ]

```

- 11. The counter readout should be  $336 \pm 1$  MHz. If the counter readout is not within tolerance, do the following:

- a. Press the following keys:

```

[ Spc! Fctn ]

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ LOCAL OSC ]

[ PRETUNE SLOPE ]

```

- b. Adjust PRETUNE SLOPE (A23 R457) for 305.6  $\pm$  0.1 MHz.

- c. Repeat steps 5 through 11 until all are within tolerance without adjustment.

- d. Press the [Preset] hardkey to exit the adjustment mode.

- 12. Disconnect the frequency counter from A21 J3.

- 13. Reconnect A21 J3 to A12 J1 and A22 J3 to A51 J1.

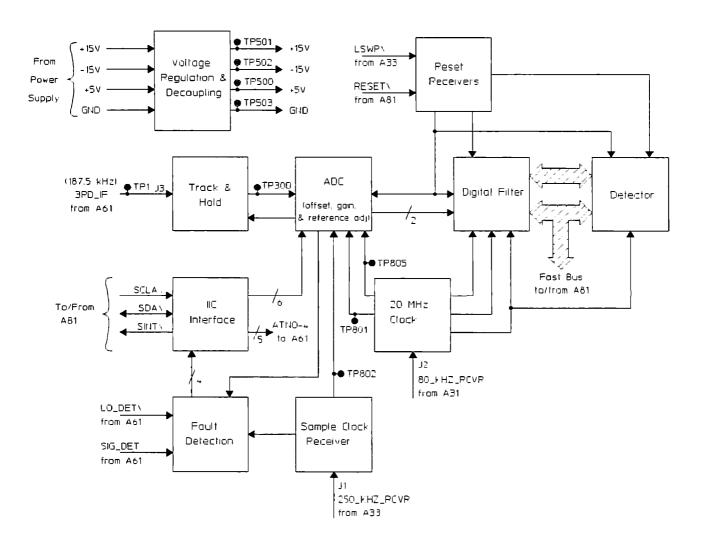

# 11. ADC Gain, Offset, and Reference

This procedure adjusts the second-pass gain, the first-pass offset, and the reference voltage for the ADC on the A62 ADC/Digital Filter assembly.

Equipment Required.

Oscilloscope

1:1 Oscilloscope Probe

Synthesizer Extender Board Extender Cables

BNC(m)-to-SMB(f) Cable

Capacitive Load BNC Cable

Note

Although a digital oscilloscope is listed in the recommended equipment list, this adjustment may be easier using an analog oscilloscope.

- 1. Set the power switch to STANDBY (a). Remove the screw at each end of the A62 ADC/Digital Filter assembly, and place the assembly on an extender board.

- 2. Reconnect A62 J1 to A33 J3 and A62 J2 to A31 J8 using extender cables. Reconnect the fast bus cable to A62 J5 using the fast bus extender cable.

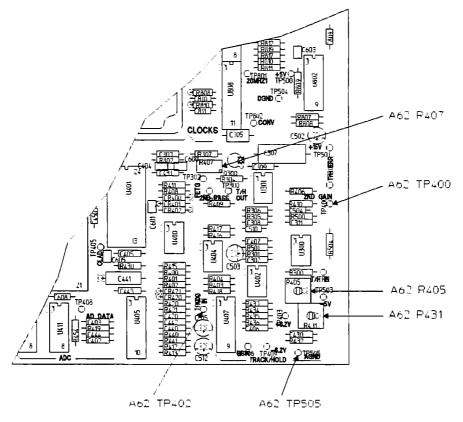

- 3. Connect the oscilloscope to A62 TP400 (see figure 1-7) using a capacitive load and a 1:1 oscilloscope probe. Connect the probe ground clip to TP 505 (AGND).

Figure 1-7. A 62 ADC/Digital Filter Component Locator

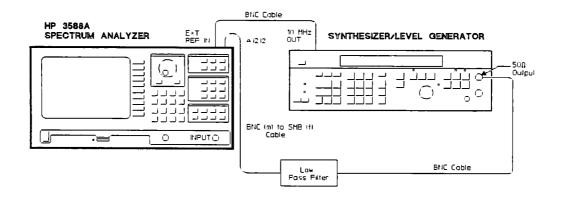

4. Connect the synthesizer to A62 J3 using a BNC-to-SMB cable.

Note

A  $50\Omega$  termination is required for synthesizers with  $50\Omega$  output impedance.

- 5. Connect the synthesizer's synchronous output to either the oscilloscope's channel 2 input or external trigger input using a BNC cable.

- 6. Set the synthesizer as follows:

Function Sine Wave

Frequency 1 kHz

Amplitude 10 mVrms

Adjustments HP 3588A

11. ADC Gain, Offset, and Reference

7. Set the oscilloscope as follows:

| Channel 1 | Volts/Div  | 20 mV/div                |

|-----------|------------|--------------------------|

|           | Offset     | 0V                       |

|           | Coupling   | $1\mathrm{M}\Omega$ ac   |

| Channel 2 | Volts/Div  | 500 mV/div               |

|           | Offset     | 0V                       |

|           | Coupling   | $1M\Omega$ ac            |

| Time Base | Time/Div   | 1.0 ms/div               |

|           | Sweep      | Triggered                |

| Trigger   | Level      | 500 mV                   |

|           | Slope      | Positive                 |

|           | Mode       | Edge                     |

|           | Source     | Channel 2 or Ext Trigger |

| Display   | Mode       | Repetitive               |

|           | Averaging  | On                       |

|           | No. of Avg | 8                        |

|           | Screen     | Single                   |

8. Set the power switch to ON (1), then press the following keys:

```

[ Spci Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ ADC ]

[ ADC 2ND PASS GAIN ]

```

- 9. Adjust A62 R407 for a flat trace on the oscilloscope display.

- 10. Remove the capacitive load from the oscilloscope, and connect the oscilloscope probe to A62 TP402.

- 11. Change the set up for the oscilloscope as follows:

| Channel 1 | Volts/Div   | 100 mV/div                         |

|-----------|-------------|------------------------------------|

|           | Coupling    | $1~\mathrm{M}\Omega~\mathrm{d}c$   |

| Channel 2 | Coupling    | $1  \mathrm{M}\Omega  \mathrm{dc}$ |

| Time Base | Time/Div    | $500 \mu\text{s/div}$              |

| Display   | Averaging   | Off                                |

|           | Persistence | 2.00s                              |

- 12. Increase the synthesizer's amplitude to 400 mVrms.

- 13. Press the [ ADC OFFSET & REFERNC ] softkey.

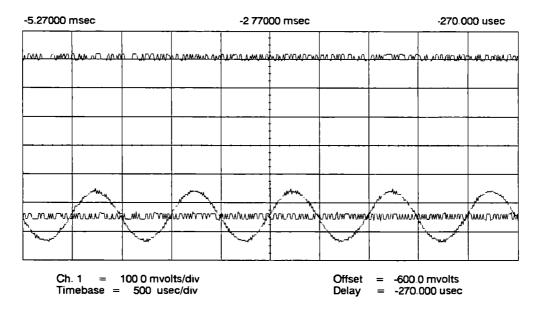

- 14. The oscilloscope display should look like figure 1-8. The following describes the signals shown on the oscilloscope display:

- A straight, horizontal line in the upper half of the display.

- A sine wave in the lower half of the display.

- A "noisy" flat trace at the center of the sine wave.

If the oscilloscope display does not look like figure 1-8, do the following:

Figure 1-8. R431 and R405 Correctly Adjusted

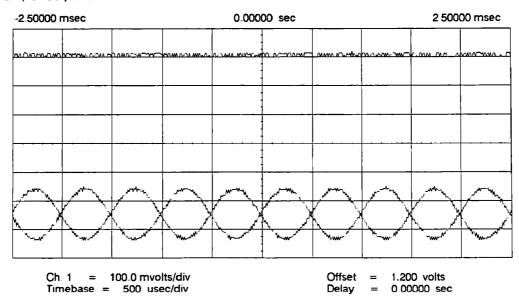

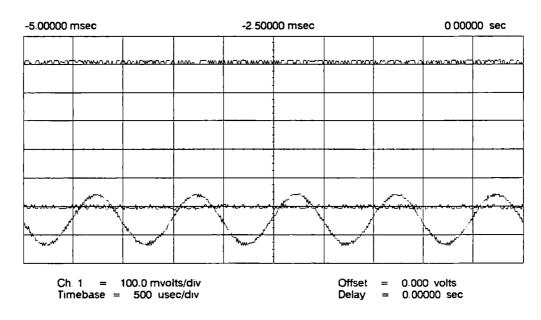

a. If the oscilloscope display looks like figure 1-9, adjust A62 R431 for a flat "noisy" trace as shown in figure 1-10.

11. ADC Gain, Offset, and Reference

Figure 1-9. R431 and R405 Incorrectly Adjusted

b. If the oscilloscope display looks like figure 1-10, adjust A62 R405 to position the flat trace at the center of the sine wave trace as shown in figure 1-8.

Figure 1-10. R405 Incorrectly Adjusted

- 15. Set the power switch to STANDBY (a). Place the ADC/Digital Filter assembly into the card nest, and replace the screws.

- 16. Reconnect the following using original cables:

A62 J1 to A33 J3 A62 J2 to A31 J8 A62 J3 to A61 J3

# 12. Second IF Bandpass Filter

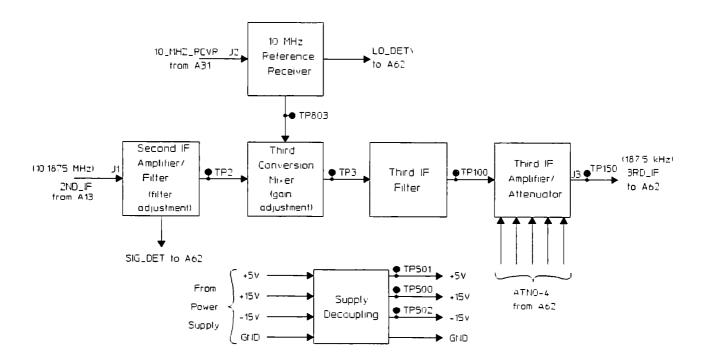

This procedure adjusts the second IF bandpass filter on the A61 IF assembly. This 10.1875 MHz bandpass filter attenuates signals outside the passband.

Equipment Required:

Spectrum Analyzer

Extender Board

Extender Cables

BNC Cable

SMB(m)-to-SMB(m) Adapter

- 1. Set the power switch to STANDBY (a). Remove the screw at each end of the A61 IF assembly, and place the assembly on an extender board.

- 2. Reconnect the following using extender cables (connecting A61 J1 to A13 J3 requires using two extender cables and an adapter):

A61 J1 to A13 J3 A61 J2 to A31 J3 A61 J3 to A62 J3

3. Set the power switch to ON (1), then press the following keys:

```

[ Spci Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ RECEIVER IF ]

[ 2nd IF1 ]

```

During this adjustment, the reference level automatically changes when the signal reaches the top or bottom of the displayed range. The analyzer beeps to indicate that the reference level changed.

4. Adjust A61 L3, L4, L5, L6, L8, L9, and L10 from the circuit side of the board (see figure 1-11 for component location) for a maximum Man readout (approximately – 20 dBm). Continue adjusting until no further improvement can be made.

Note

If the signal is below the displayed range, continue to adjust. The signal is not seen when the filter is too far out of adjustment.

Figure 1-11. A61 IF Component Locator

- 5. Press the [ 2nd IF2 ] softkey.

- 6. Connect REF OUT (10 MHz) on the rear panel to INPUT on the front panel using a BNC cable.

- 7. Adjust A61 C30 for a minimum Man readout.

- 8. Press the [2nd IF3] softkey.

- 9. Alternately adjust A61 L4 and L5 for a maximum Man readout.

- 10. Press the [2nd IF4] softkey.

Adjustments HP 3588A

### 12 Second IF Bandpass Filter

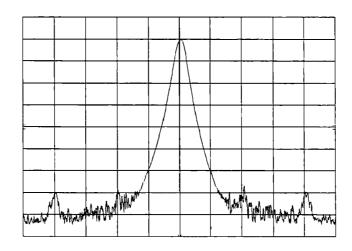

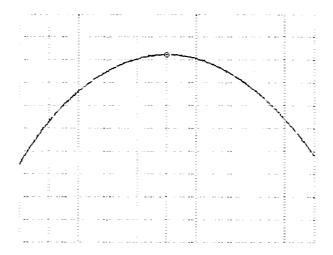

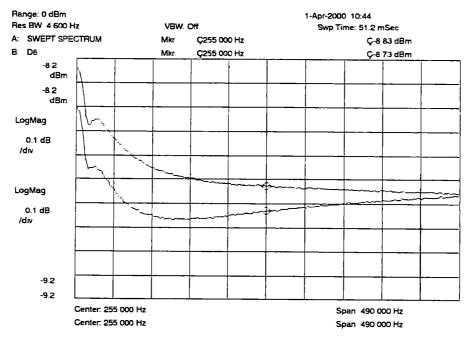

11. Alternately adjust A61 L4 and L5 to center the peak and equalize the level of the sides (see figure 1-12).

Figure 1-12. Second IF Adjustment

12. Set the spectrum analyzer as follows:

$\begin{array}{lll} \text{Input} & 1 \text{ M}\Omega \\ \text{Center Frequency} & 187.5 \text{ kHz} \\ \text{Span} & 10 \text{ kHz} \\ \text{Scale} & 0 \text{ dBV} \end{array}$

- 13. Connect the spectrum analyzer to A61 TP3 using a 1:1 oscilloscope probe.

- 14. Press the [ 2nd IF5 ] softkey.

- 15. Adjust A61 R11 for  $-32.0 \pm 0.1$  dBV.

- 16. Set the power switch to STANDBY (6). Place the IF assembly into the card nest, and replace the screws.

- 17. Reconnect the following using original cables:

A61 J1 to A13 J3

A61 J2 to A31 J3

A61 J3 to A62 J3

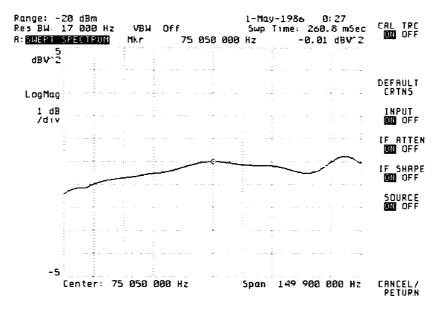

### 13. Source Bandpass Filter

This procedure adjusts the four cavity helical resonator filter on the A42 Source Conversion assembly. This 310.1875 MHz bandpass filter attenuates signals outside of its narrow passband.

Equipment Required:

Extender Board

**Extender Cables**

1. Set the power switch to STANDBY (a). Remove the screw at each end of the A42 Source Conversion assembly, and remove the assembly from the card nest.

#### Caution

To avoid damaging the cables connected to A33 J5 and J6, disconnect and position the cables away from the A42 Source Conversion assembly before removing or inserting the A42 Source Conversion assembly.

2. Remove the shield can covering A42 W202 and W203 (see figure 1-13). Move A42 W201, W202, and W203 to their test positions.

justments HP 3588A

Figure 1-13. A42 Source Conversion Component Locator

3. Remove the plate covering the helix cavity. Then using a ball driver hex tool, turn all four tuning screws (CAV ADJ 1, 2, 3, and 4) clockwise until the screws just contact the helix structure inside the cavity (see caution below). Replace the plate covering the helix cavity.

### Caution

The helix structure will be damaged if the tuning screws are turned in too far. Be careful to only turn the screws until they just touch the helix structure inside the cavity.

- 4. Place the A42 Source Conversion assembly on an extender board.

- 5. Reconnect the following using extender cables:

A42 J1 to A41 J3

A42 J2 to A21 J2

A42 J3 to A32 J3

A42 J4 to A31 J5

A42 J6 to A33 J2

A52 J2 to A33 J4

A62 J1 to A33 J3

6. Set the power switch to ON (1), then press the following keys:

```

[ Spci Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ SOURCE ]

[ HELICAL RESONATOR ]

```

# Note

During this adjustment, the reference level automatically changes when the signal reaches the top or bottom of the displayed range. The analyzer beeps to indicate that the reference level changed.

- 7. Adjust CAV ADJ 1 counterclockwise for a maximum signal level.

- 8. Adjust CAV ADJ 2 counterclockwise for a minimum signal level. (The minimum level should be about 15 dB smaller than the maximum level achieved in the previous step.)

- 9. Adjust CAV ADJ 3 counterclockwise for a maximum signal level.

- 10. Adjust CAV ADJ 4 counterclockwise for a minimum signal level.

- 11. Set the power switch to STANDBY (a). Return W201, W202, and W203 to their original positions. Replace the shield can.

- 12. Place the Source Conversion assembly into the card nest, and replace the screws.

- 13. Reconnect the following using original cables:

```

A42 J1 to A41 J3

```

A42 J2 to A21 J2

A42 J3 to A32 J3

A42 J4 to A31 J5

A42 J6 to A33 J2

A52 J2 to A33 J4

A62 J1 to A33 J3

A33 J5 to TRIG OUT (white cable)

A33 J6 to EXT TRIG (black cable)

## 14. First IF Bandpass Filter

This procedure adjusts the four cavity helical resonator filter on the A12 First Conversion assembly. This 310.1875 MHz bandpass filter attenuates signals outside of its narrow passband.

Equipment Required:

Extender Board

**Extender Cables**

- 1. Set the power switch to STANDBY (a). Remove the screw at each end of the A12 First Conversion assembly, and remove the assembly from the card nest.

- 2. Move A12 W801, W802, and W803 to their test positions (see figure 1-14).

Figure 1-14. A12 First Conversion Component Locator

3. Remove the plate covering the helix cavity. Then using a ball driver hex tool, turn all four tuning screws (CAV ADJ 1, 2, 3, and 4) clockwise until the screws just contact the helix structure inside the cavity (see caution below). Replace the plate covering the helix cavity.

### Caution

The helix structure will be damaged if the tuning screws are turned in too far. Be careful to only turn the screws until they just touch the helix structure inside the cavity.

- 4. Place the assembly on an extender board.

- 5. Reconnect the following using extender cables:

A12 J1 to A21 J3 A12 J2 to A11 J3 A12 J3 to A13 J2

6. Set the power switch to ON (1), then press the following keys:

```

[ Spci Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ RECEIVER IF ]

[ HELICAL RESONATOR ]

```

# Note

During this adjustment, the reference level automatically changes when the signal reaches the top or bottom of the displayed range. The analyzer beeps to indicate that the reference level changed.

- 7. Adjust CAV ADJ 1 counterclockwise for a maximum signal level.

- 8. Adjust CAV ADJ 2 counterclockwise for a minimum signal level. (The minimum level should be about 15 dB smaller than the maximum level achieved in the previous step.)

- 9. Adjust CAV ADJ 3 counterclockwise for a maximum signal level.

- 10. Adjust CAV ADJ 4 counterclockwise for a minimum signal level.

Adjustments HP 3588A

### 14. First IF Bandpass Filter

11. Set the power switch to STANDBY (a). Return W801, W802, and W803 to their original positions.

- 12. Place the First Conversion assembly into the card nest, and replace the screws.

- 13. Reconnect the following using original cables:

A12 J1 to A21 J3 A12 J2 to A11 J3 A12 J3 to A13 J2

### 15. Autorange Threshold Adjustment

Equipment Required:

Frequency Synthesizer

Extender Board Extender Cables

BNC(m) to SMB(f) Cable SMB(m) to SMB(m) Adapter

- 1. Set the power switch to STANDBY (a). Remove the screw at each end of the A11 Input assembly, and remove the assembly from the cardnest

- 2. Using the BNC-to-SMB cable and adapter, connect the frequency synthesizer to A11 J4 (SMB connector at the bottom of the A11 assembly). Place the assembly on an extender board.

- 3. Turn A11 R626 fully counterclockwise.

- 4. Reconnect the following using extender cables:

```

A11 J1 to A41 J1

A11 J2 to A31 J1

A11 J3 to A12 J2

```

5. Set the power switch to ON (1), wait for the calibration to complete, then press the following keys:

```

[ SpcI Fctn ]

[ AUTO CAL OFF ]

[ Range/input ]

[ RANGE ]

- 20

[ dBm ]

```

- 6. Set the frequency synthesizer for a 10 MHz, 18.5 dBm sine wave output.

- 7. Adjust A11 R624 so that A11 CR606 just lights up, indicating that the upper threshold trip point was reached. (Turn A11 R624 counterclockwise to light A11 CR606.)

- 8. Change the frequency synthesizer amplitude to -31.5 dBm.

- 9. Adjust A11 R626 so that A11 CR607 just lights up, indicating that the lower threshold trip point was reached. (Turn A11 R626 clockwise to light A11 CR607.)

- 10. Set the power switch to STANDBY (a). Place the A11 Input assembly into the cardnest, and replace the screws.

- 11. Reconnect the following using the original cables:

A11 J1 to A41 J1 A11 J2 to A31 J1 A11 J3 to A12 J2

## 16. 1 Meg Ohm Flatness

This procedure adjusts the flatness of the frequency response of the 1 M $\Omega$  buffer on the A11 Input assembly.

Equipment Required:

Extender Board

**Extender Cables**

Small Adjustment Tool

$50\Omega$  Feedthrough Termination BNC(m)-to-SMB(f) Cable SMB(m)-to-SMB(m) Adapter

- 1. Set the power switch to STANDBY (a). Remove the screw at each end of the A11 Input assembly, and remove the assembly from the card nest.

- 2. Connect the 50Ω feedthrough termination to the SOURCE connector. Using the BNC-to-SMB cable and adapter, connect the feedthrough termination to A11 J4 (SMB connector at bottom of A11 Input assembly). Place the assembly on an extender board.

- 3. Reconnect the following using extender cables:

A11 J1 to A41 J1 A11 J2 to A31 J1 A11 J3 to A12 J2

4. Set the power switch to ON (1), then press the following keys:

```

[ SpcI Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ RECEIVER INPUT ]

[ 1 MOHM FLATNESS ]

```

Figure 1-15. A11 Input Component Locator

5. Using the small adjustment tool in the service kit, adjust A11 C413 through a hole in the shield can so the displayed waveforms are as close as possible without the ends crossing (see figure 1-16).

Figure 1-16. 1 Meg Ohm Flatness Adjustment

- 6. Set the power switch to STANDBY (b). Place the Input assembly into the card nest, and replace the screws.

- 7. Reconnect the following using original cables:

A11 J1 to A41 J1 A11 J2 to A31 J1 A11 J3 to A12 J2

## 17. Oven Frequency

This procedure adjusts the frequency of option 001, A91 Fan Power/Oven assembly. The A91 Fan Power/Oven assembly provides the HP 3588A Spectrum Analyzer with an absolute frequency reference.

Equipment Required:

Oscilloscope

Frequency Standard

**BNC Cable**

Note

The HP 3588A Spectrum Analyzer must be warmed up for at least 48 hours before this adjustment is made.

- 1. Remove the screw on the oven-adjustment cover. Lift the screw side of the oven-adjustment cover and tilt back to the open position.

- 2. Connect the frequency standard's output to the oscilloscope's external trigger (make sure the frequency standard is properly terminated).

- 3. Connect OVEN REF OUT (located on the rear panel) to the oscilloscope's channel 1 input.

- 4. Adjust FINE FREQUENCY ADJUST (A91 R12) to the center of its adjustment range.

- 5. Set the oscilloscope as follows:

| Channel 1 | Volts/Div   | 500 <b>mV/di</b> v |

|-----------|-------------|--------------------|

|           | Offset      | $0\mathbf{V}$      |

|           | Coupling    | $1  M\Omega$ ac    |

| Timebase  | Time/Div    | 50 ns/div          |

|           | Sweep       | Triggered          |

| Trigger   | Level       | $0\mathbf{V}$      |

|           | Slope       | Positive           |

|           | Mode        | Edge               |

|           | Source      | External Trigger   |

| Display   | Mode        | Repetitive         |

|           | Averaging   | Off                |

|           | Persistence | 500 ms             |

|           | Screen      | Single             |

Adjustments HP 3588A

### 17. Oven Frequency

6. Remove the oven screw and adjust COARSE FREQUENCY ADJUST (A91 U3) for a stable (not moving) display on the oscilloscope.

- 7. Change the oscilloscope timebase to 10 ns per division.

- 8. Adjust FINE FREQUENCY ADJUST for a stable (not moving) display on the oscilloscope.

- 9. Return the oven screw, oven-adjustment cover and screw, and rear panel jumper (OVEN REF OUT to EXT REF IN) to their original positions.

### 18. Calibrator Flatness and Level

This procedure adjusts the level and flatness of the calibration signal on the A31 Reference/Calibrator assembly.

**Equipment Required:**

Milliwatt Power Meter (recommended)

or Power Meter (alternate)

**BNC** Cable

N(f)-to-BNC(f) Adapter

# Note

This adjustment can be done with either a milliwatt power meter or a standard power meter. For best accuracy, use the milliwatt power meter.

1. Connect the power meter to the SOURCE connector (located on front panel) using the N-to-BNC adapter and BNC cable.

# **Note**

If you are using a standard power meter, set its calibration factor for 300 kHz to improve the accuracy of this adjustment.

2. Press the following keys:

```

[SpcI Fctn]

ſ

(second softkey from bottom)

- 99

(second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ ADJUSTMTS ]

[ CALIBRATR ]

[ CAL LEVEL ]

```

- 3 After the message appears on the screen, press the [SRCE DAC ATTEN] softkey and adjust the attenuation level for a  $0 \text{ dBm} \pm 0.01 \text{ dB}$  readout on the power meter.

- 4. Press the [NEXT STEP] softkey.

- 5. Disconnect the BNC cable from the power meter and connect to the INPUT connector (SOURCE connected to INPUT).

- 6. After the Man readout is stable, press the [ NEXT STEP ] softkey.

Adjustments HP 3588A

#### 18. Calibrator Flatness and Level

7. While monitoring the Man readout, adjust CAL LEVEL (A31 R322) for the value indicated in the message on the display.

8. Disconnect the BNC cable from the INPUT connector and reconnect to the power meter (SOURCE connected to power meter).

If you are using a standard power meter, set its calibration factor for 120 MHz to improve the accuracy of this adjustment.

- 9. Press the [ CAL FLATNESS ] softkey.

- 10. After the message appears on the screen, press the [SRCE DAC ATTEN] softkey and adjust the attenuation level for a 0 dBm  $\pm$  0.01 dB readout on the power meter.

- 11. Press the [ NEXT STEP ] softkey.

- 12. Disconnect the BNC cable from the power meter and reconnect to the INPUT connector (SOURCE connected to INPUT).

- 13. After the Man readout is stable, press the [ NEXT STEP ] softkey.

- 14. While monitoring the Man readout, adjust CAL FLAT (A31 C330) for the value indicated in the message on the display.

- 15. Disconnect the cable connected between the SOURCE connector and INPUT connector.

- 16. Press the [Preset] hardkey to exit the adjustment mode.

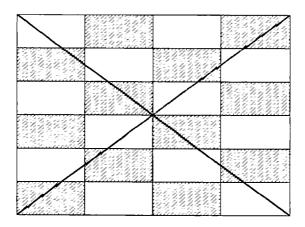

# 19. Display

This procedure adjusts the focus, intensity, and alignment of the Display assembly.

Equipment Required:

None

Note

If the Display assembly needs to be adjusted, adjust only the components that apply to the problem.

1. Press the following keys to view the test pattern:

```

[ Spci Fctn ]

[ ] (second softkey from bottom)

- 99

[ ] (second softkey from bottom)

[ SERVICE FUNCTIONS ]

[ SELF TEST ]

[ FUNCTIONL TESTS ]

[ DISPLAY ]

[ TEST PATTERN ]

```

2. Compare the test pattern to figure 1-17 and adjust as indicated in table 1-3.

Figure 1-17. Center Portion of Display Test Pattern

Table 1-3. Display Adjustments

| Adjustment Name     | Adjust for                                                       |  |  |

|---------------------|------------------------------------------------------------------|--|--|

| Focus               | Optimum focus                                                    |  |  |

| Brightness          | Optimum intensity                                                |  |  |

| Horizontal Width †  | Test pattern width of 6.89 $\pm$ 0.06 inches (175 $\pm$ 1.5 mm)  |  |  |

| Vertical Hold       | Vertically stable display                                        |  |  |

| Vertical Linearity  | Uniform height of blocks in test pattern                         |  |  |

| Vertical Position   | Vertically centered test pattern                                 |  |  |

| Vertical Size       | Test pattern height of 4.92 $\pm$ 0.06 inches (128 $\pm$ 1.5 mm) |  |  |

| Horizontal Position | Horizontally centered test pattern                               |  |  |

| Horizontal Hold     | Horizontally stable display                                      |  |  |

<sup>†</sup> Adjust using non-metallic hexagonal tuning tool.

If Vertical Linearity is adjusted, check Vertical Size and Vertical Position, and adjust if necessary.

3. Press the [Preset] hardkey to exit the adjustment mode.

# Section II

# Replaceable Parts

### Introduction

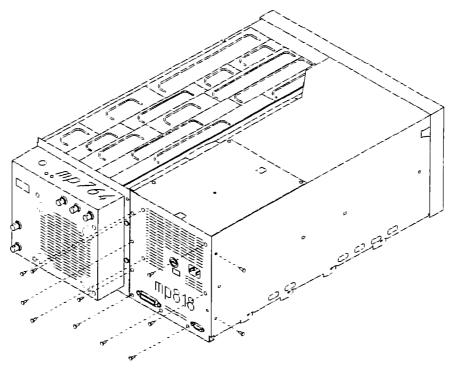

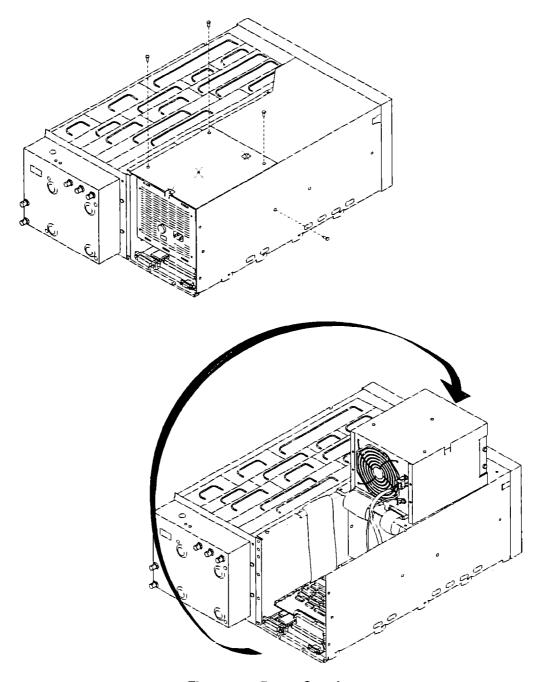

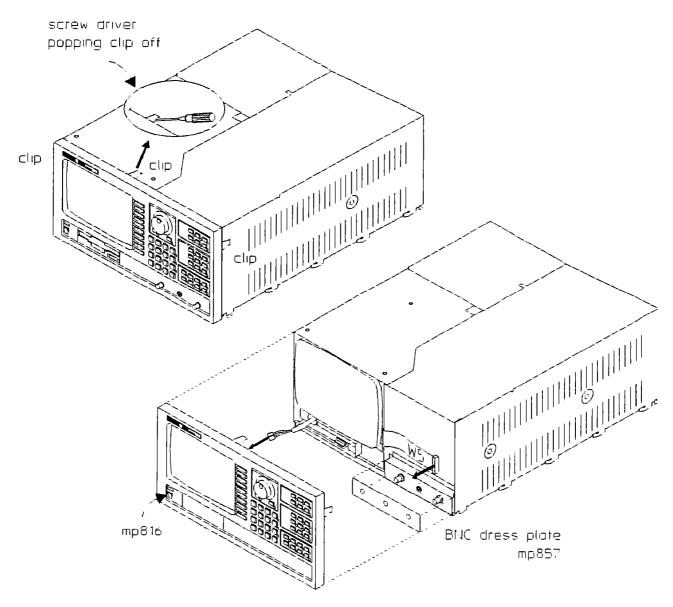

This section contains information for ordering replacement parts for the HP 3588A Spectrum Analyzer. This section also contains illustrations showing how to disassembly and assembly the analyzer. These illustrations also show reference designator numbers for the hardware.

Replacement parts are listed in the following three tables:

- Assemblies

- Cables

- Hardware

#### Caution

Many of the parts listed in this section are static sensitive. Use the appropriate precautions when removing, handling, and installing all parts to avoid unnecessary damage.

### **Ordering Information**

# Note

See the final pages in the back of this manual for a list of Hewlett-Packard sales and service office locations and addresses.

### **Ordering Non-Listed Parts**

To order a part that is NOT listed in the replaceable parts tables, indicate the instrument model number, instrument serial number, description and function of the part, and the quantity of the part required. Address the order to the nearest Hewlett-Packard sales and service office.

### **Direct Mail Order System**

Within the U.S.A., Hewlett-Packard can supply parts through a direct mail order system. Advantages of the Direct Mail Order System are:

- Direct ordering and shipment from the HP Parts Center.

- No maximum or minimum on any mail order. There is a minimum order for parts ordered through a local HP sales and service office when the orders require billing and invoicing.

- Transportation charges are prepaid. A small handling charge is added to each order.

- No invoicing. A check or money order must accompany each order.

- Mail order forms and specific ordering information are available through your local Hewlett-Packard sales and service office.

Table 2-1. Abbreviations Used

| Al aluminum A ampere(s) Au gold cer ceramic coef coefficient com common conn dep deposited DPDT double-pole double-throw DPST double-pole single-throw elect electrolytic encap encapsulated F farad(s) FET field effect transistor fixd fixed GaAs* gallium arsenide GHz NPO nn NP | neon normally open negative positive zero (zero temperature coefficient) nanosecond(s) = 10 <sup>-9</sup> seconds not separately replaceable order by description outside diameter peak printed circuit picofarad(s) 10 <sup>-12</sup> farads peak inverse voltage part of position(s) polystyrene potentiometer peak-to-peak parts per million |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Al aluminum A ampere(s) Au gold cer ceramic coef coefficient com common conn dep deposited DPDT double-pole double-throw DPST double-pole single-throw elect electrolytic encap encapsulated F farad(s) FET field effect transistor fixd fixed GaAs* gallium arsenide GHz NPO nn NP | normally open negative positive zero (zero temperature coefficient) nanosecond(s) = 10 <sup>-9</sup> seconds not separately replaceable order by description outside diameter peak printed circuit picofarad(s) 10 <sup>-12</sup> farads peak inverse voltage part of position(s) polystyrene potentiometer peak-to-peak                        |

| A ampere(s)  Au gold (cer ceramic ns msr more coef coefficient nsr msr msr msr msr msr msr msr msr msr m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | negative positive zero (zero temperature coefficient) nanosecond(s) = 10 <sup>-9</sup> seconds not separately replaceable order by description outside diameter peak printed circuit picofarad(s) 10 <sup>-12</sup> farads peak inverse voltage part of position(s) polystyrene potentiometer peak-to-peak                                      |

| Au gold  cer ceramic ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (zero temperature coefficient) nanosecond(s) = 10 <sup>-9</sup> seconds not separately replaceable order by description outside diameter peak printed circuit picofarad(s) 10 <sup>-12</sup> farads peak inverse voltage part of position(s) polystyrene potentiometer peak-to-peak                                                             |

| cer ceramic ns ns ns coefficient nsr obd com common obd oconn connection dep deposited p p p p p p p p p p p p p p p p p p p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nanosecond(s) = 10 <sup>-9</sup> seconds not separately replaceable order by description outside diameter peak printed circuit picofarad(s) 10 <sup>-12</sup> farads peak inverse voltage part of position(s) polystyrene potentiometer peak-to-peak                                                                                            |

| coef coefficient nsr obd com com common obd obd conn connection OD obd connection dep deposited properties of the composite o | not separately replaceable order by description outside diameter peak printed circuit picofarad(s) 10 <sup>-12</sup> farads peak inverse voltage part of position(s) polystyrene potentiometer peak-to-peak                                                                                                                                     |

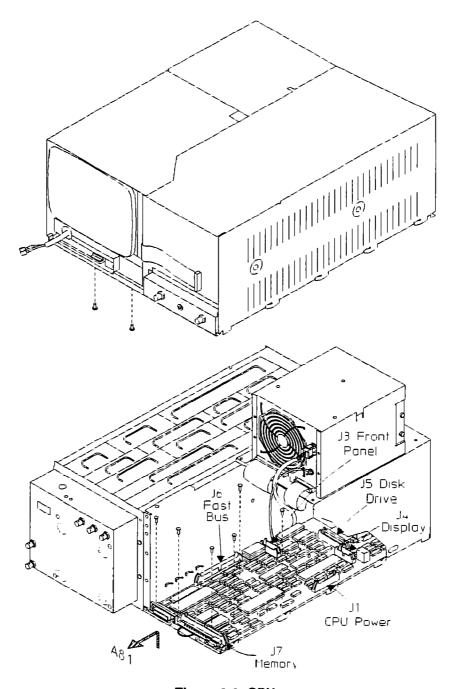

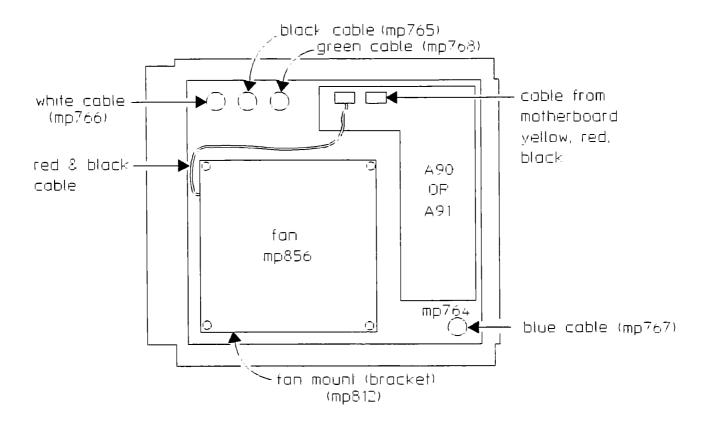

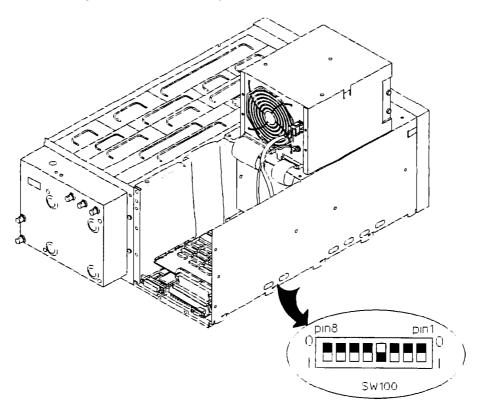

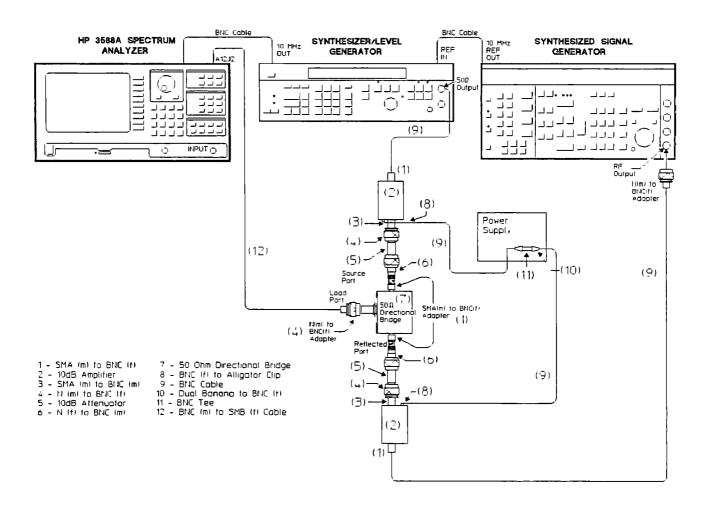

| com common obd oconn connection oDD oconn dep deposited properties of the connection odd objection oconnection odd objective of the connection oconnection objective objective of the connection oconnection objective objective oconnection oconnection objective or properties of the connection oconnection objective or properties of the connection of the connection objective or properties of the connection of the connecti | order by description outside diameter peak printed circuit picofarad(s) 10 <sup>-12</sup> farads peak inverse voltage part of position(s) polystyrene potentiometer peak-to-peak                                                                                                                                                                |